Achronix Semiconductor a récemment annoncé la disponibilité générale du FPGA Speedster7t AC7t1500 conçu pour les applications d’accélération de réseau, de stockage et de calcul (AI/ML).

La famille de FPGA Speedster7t 7 nm offre des ports PCIe Gen5 et des interfaces mémoire GDRR6 et DDR5/DDR4, fournit jusqu’à 400 Gbit/s sur les ports Ethernet et comprend un réseau 2D sur puce (2D NoC) qui peut gérer 20 Tbit/s de bande passante totale.

Points forts d’Achronix Speedster7t :

- Réseau bidimensionnel sur puce (2D NoC) permettant un flux de données à large bande passante à travers et entre la structure FPGA et les contrôleurs et interfaces d’E/S matérielles et de mémoire

- Blocs MLP (Machine Learning Processors) avec des tableaux de multiplicateurs, des arbres d’additionneurs, des accumulateurs et la prise en charge des opérations à virgule fixe et flottante, y compris la prise en charge directe du format bfloat16 de Tensorflow et du format de bloc à virgule flottante (BFP).

- Plusieurs ports PCIe Gen5

- Émetteurs-récepteurs SerDes à haut débit, prenant en charge la modulation PAM4 112 Gbit/s et la modulation PAM4/NRZ 56 Gbit/s, ainsi que des débits de données inférieurs

- MAC Ethernet dur prenant en charge jusqu’à 400 Gbit/s

- Contrôleurs et interfaces SDRAM GDDR6 et DDR5 (Remarque : le Speedster7t AC7t1500 prend en charge la DDR4 plutôt que la DDR5)

- Sécurité

- Moteur cryptographique bidirectionnel basé sur la structure (Speedster7t AC7t1550)

- Moteur cryptographique bidirectionnel dur (Speedster7t AC7t800 et autres)

- Architecture logique avec des LUT à 6 entrées (6LUT), des ALU à 8 bits, des bascules et un mode LUT multiplicateur reformulé (MLUT) basé sur un algorithme de Booth modifié, qui double les performances de la multiplication basée sur la LUT

- Routage de matrice amélioré avec routage de bus dédié et multiplexage de bus actif

- Blocs de mémoire BRAM de 72 Ko et LRAM de 2 Ko

- GPIO prenant en charge plusieurs normes d’E/S

- PLL et DLL pour prendre en charge plusieurs arbres d’horloge sur puce

- Plusieurs types d’interfaces de programmation

- Reconfiguration partielle du tissu FPGA

- Mise à jour à distance de la matrice FPGA

- Fonctions de sécurité pour chiffrer et authentifier les flux binaires

- Prise en charge du débogage via Achronix Snapshot

Il y a cinq parties dans la matrice de produits Speedster7t avec le 7t1500 avec 692K LUTs maintenant en production de masse et le 7t800 d’entrée de gamme avec 326 LUTs qui vient d’être ajouté à Achronix Tool Suite. Les pièces haut de gamme 7t3000 et 7t6000 doivent être planifiées pour l’avenir car elles ne sont pas encore répertoriées dans la fiche technique.

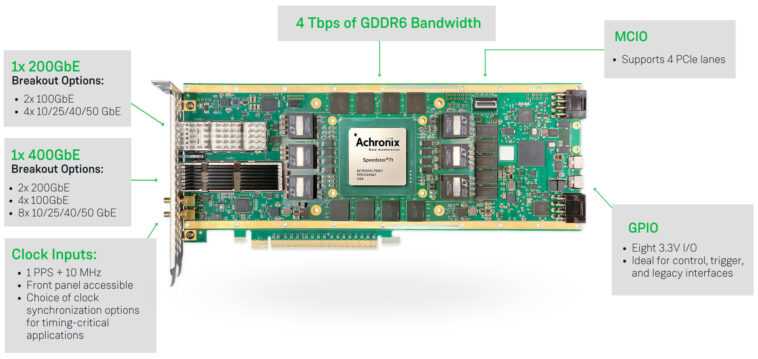

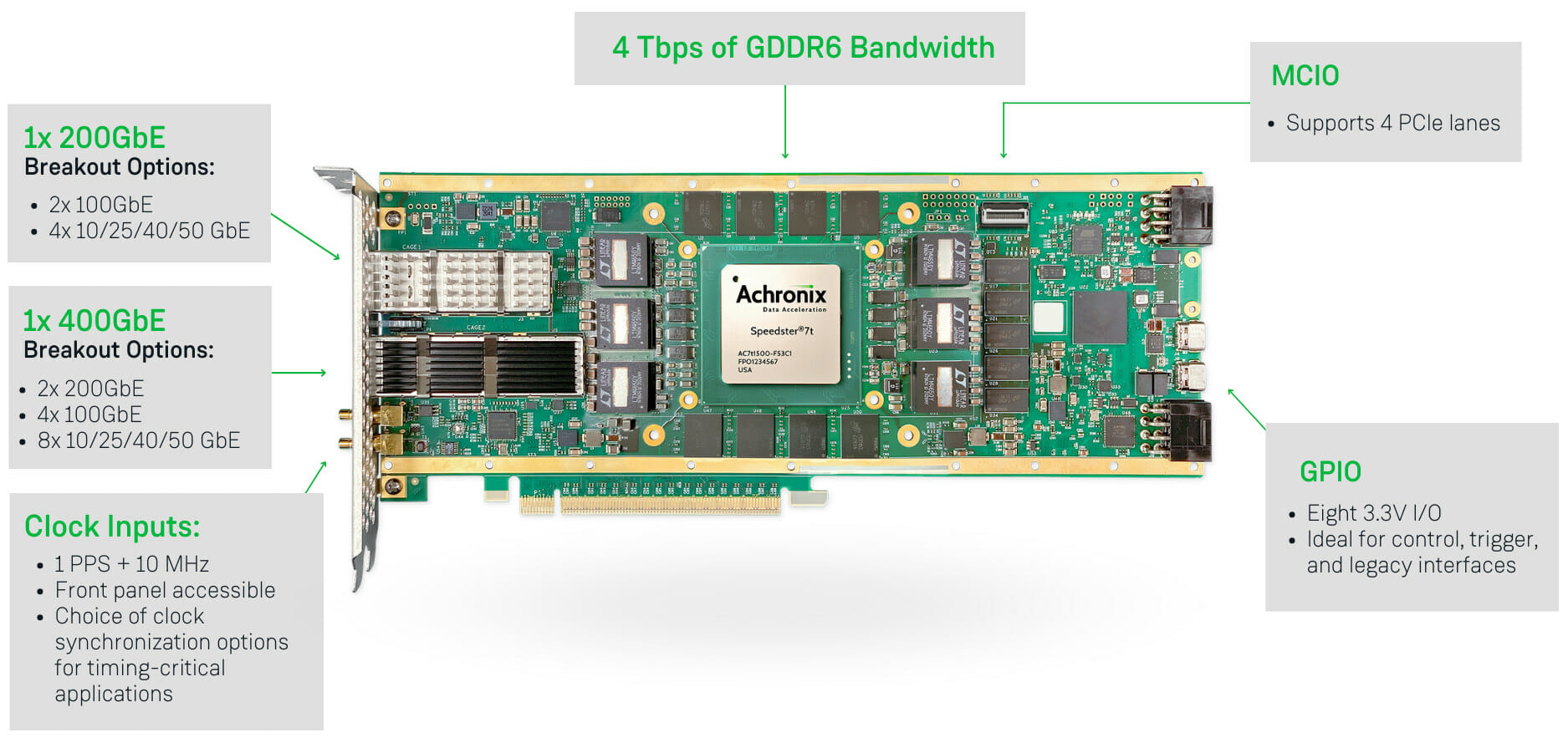

Je n’ai trouvé aucune carte de développement typique pour les FPGA Speedster7t, mais la société fournit la carte accélératrice VectorPath S7t-VG6 basée sur le FPGA 7t1500. Il est conçu pour le développement de fonctions de calcul et d’accélération hautes performances pour l’intelligence artificielle (IA), l’apprentissage automatique (ML), la mise en réseau et les applications de centre de données.

Principales interfaces et spécifications :

- FPGA – FPGA Speedster7t AC7t1500

- Mémoire système

- GDDR6 – 16 Go, 8 banques avec deux canaux 16 bits indépendants par banque

- Une banque de DDR4 – 2666 MHz avec ECC, jusqu’à 4 Go (×72)

- Stockage – Mémoire flash pour le démarrage du FPGA

- Certifié PCI SIG pour prendre en charge l’interface hôte PCIe Gen4 x16

- 1x cage QSFP-DD – 1x 400GbE, 2x 200GbE, 4x 100GbE ou 8x 10/25/40/50 GbE

- 1x cage QSFP56 – 1x 200GbE, 2x 100GbE ou 4x 10/25/40/50 GbE

- 8x GPIO

- MCIO – connecté au FPGA via quatre émetteurs-récepteurs prenant en charge jusqu’à des débits de données PCIe Gen5

La suite d’outils Achronix est utilisée pour toutes les solutions IP FPGA et eFPGA d’Achronix et est fournie avec les outils de conception ACE de la société et Synopsys Synplify-Pro pour la synthèse des conceptions FPGA. Les bibliothèques de simulation Achronix sont prises en charge par Mentor Graphics ModelSim, Synopsys VCS et Aldec Riviera-PRO, et la suite comprend également l’outil de débogage de conception en temps réel Snapshot Debugger. Le défaut de conception devrait être simple pour les concepteurs de FPGA habitués à travailler sur des FPGA concurrents prenant en charge les entrées VHDL et Verilog et la simulation standard de l’industrie.

Des informations supplémentaires peuvent être trouvées sur la page du produit et le communiqué de presse.

Merci à TLS pour le conseil.

Soutenez le logiciel Raspberryme ! Faire un don via crypto-monnaies ou alors devenir mécène sur Patreon