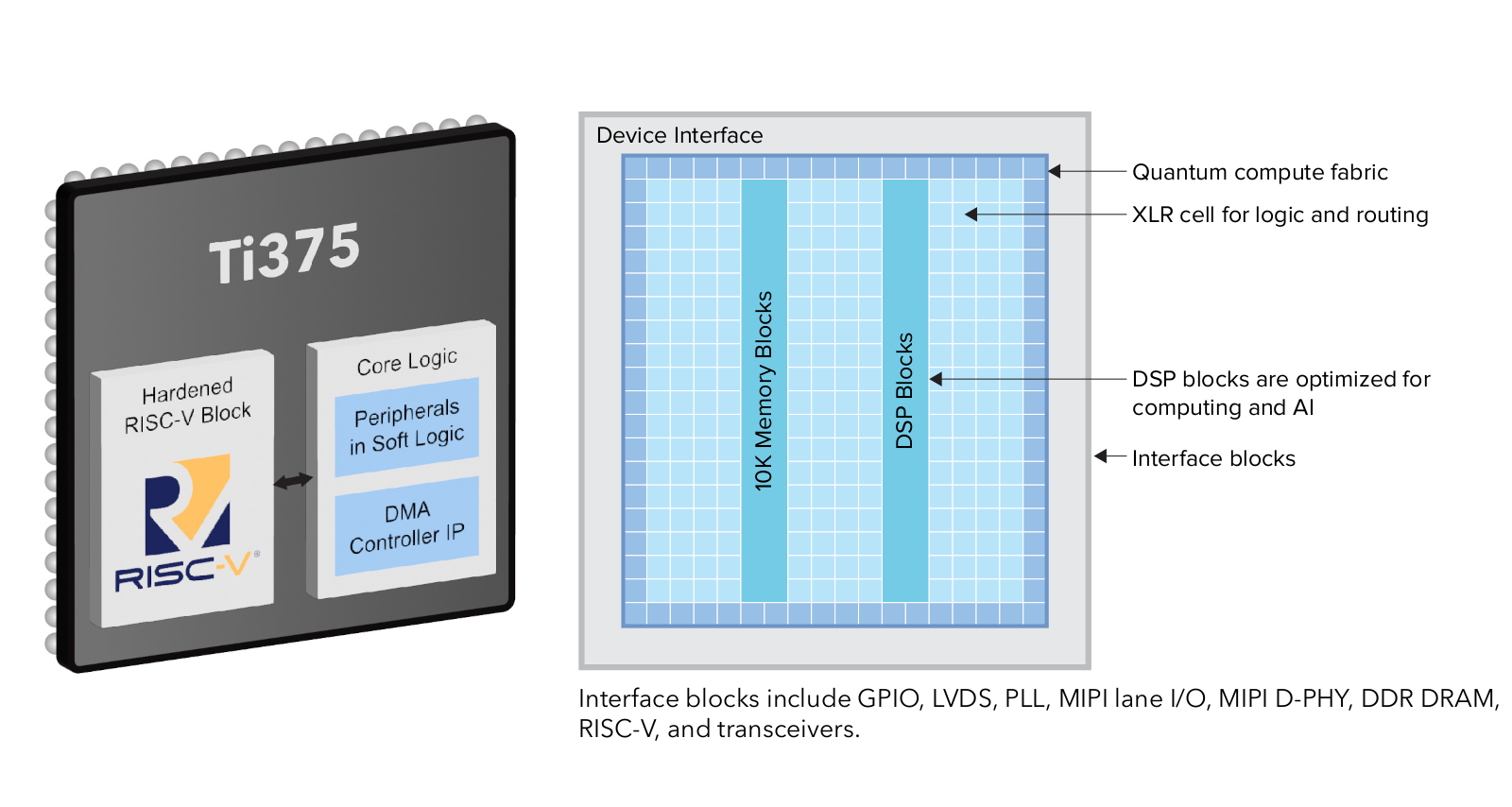

Le SoC Efinity Titanium Ti375 combine une structure informatique quantique haute densité et faible consommation avec un bloc RISC-V 32 bits renforcé quadricœur et comprend un contrôleur DRAM LPDDR4, un MIPI D-PHY pour les écrans ou les caméras et des émetteurs-récepteurs 16 Gbit/s permettant Interfaces PCIe Gen 4 et 10GbE.

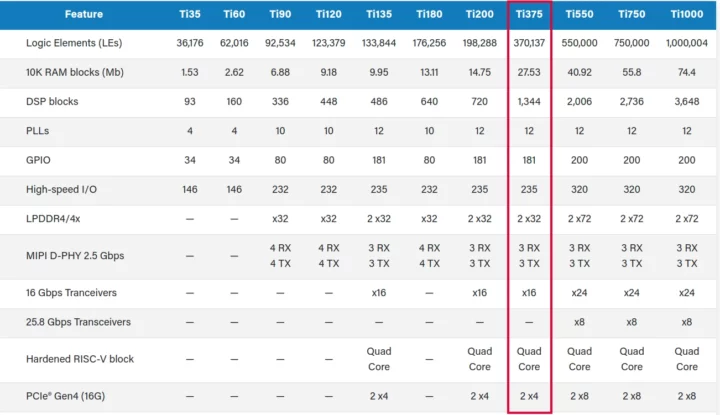

Le Titanium Ti375 est également livré avec 370 000 éléments logiques, 1 344 blocs DSP, 2 688 blocs SRAM de 10 Ko et 27,53 Mbits de mémoire intégrée, ainsi que des blocs DSP optimisés pour les charges de travail informatiques et IA, et des cellules XLR (eXchangeable Logic and Routing). pour la logique et le routage.

Spécifications de l’Efinix Titanium Ti375 :

- Structure de calcul FPGA

- 370 137 éléments logiques (LE)

- 362 880 cellules de logique et de routage échangeables (XLR)

- Mémoire embarquée de 27,53 Mbits

- 2 688 blocs SRAM de 10 Kbits

- 1 344 blocs DSP intégrés pour la multiplication, l’addition, la soustraction, l’accumulation et jusqu’à 15 bits de décalage variable vers la droite

- Mémoire – SRAM intégrée haute vitesse de 10 kbits, configurable en tant que RAM à port unique, RAM simple à double port, véritable RAM à double port ou ROM

- Blocs d’interface FPGA

- Bloc RISC-V renforcé quadricœur 32 bits (RISCV32I avec extensions M, A, C, F et D et six étages de pipeline)

- 4 banques d’émetteurs-récepteurs à grande vitesse, chacune avec 4 voies :

- Prise en charge de débits de données de 1,25 Gbit/s à 16 Gbit/s par canal

- PCIe Gen4 x4

- Conforme aux spécifications PCIe 4.0, 3.2, 2.1 et 1.1

- Prise en charge des configurations x1, x2 et x4

- Configurer en tant que port root (RP) ou point final (EP)

- Virtualisation des E/S à root unique (SRIOV)

- Prend en charge les protocoles SGMII et 10GBase-KR ainsi que PMA Direct

- 2 interfaces LPDDR4/LPDDR4x PHY (prenant en charge les largeurs DQ x32) avec IP matérielle du contrôleur de mémoire

- 3 interfaces MIPI D-PHY RX et TX avec des vitesses allant jusqu’à 2,5 Gbit/s

- 2x Deux variétés de broches d’E/S à usage général (GPIO) :

- E/S haute tension (HVIO) – Blocs d’E/S simples prenant en charge les normes d’E/S asymétriques LVTTL et LVCMOS à 1,8, 2,5 et 3,3 V.

- E/S haute vitesse (HSIO) – Blocs d’E/S configurables complexes

- E/S asymétriques et différentielles

- LVDS, subLVDS, Mini-LVDS et RSDS (RX, TX et bidirectionnel) jusqu’à 1,5 Gbit/s

- Voies MIPI (DSI et CSI) à 1,5 Gbit/s en modes haute vitesse et faible consommation, jusqu’à 1,5 Gbit/s

- 1x oscillateur

- PLL à synchronisation à spectre étalé (SSC)

- Synchronisation sur puce

- Réseau mondial à faible biais prenant en charge 32 signaux d’horloge ou de contrôle

- Réseaux d’horloges régionaux et locaux

- Jusqu’à 12x PLL avec prise en charge de la division fractionnaire N, du cycle de service programmable, de la synchronisation à spectre étalé et de la reconfiguration dynamique

- Configuration de l’appareil

- Interface SPI standard (active, passive et guirlande)

- Interface JTAG

- Prend en charge la reconfiguration interne

- Fonction de détection de perturbation à événement unique (SEU)

- Fonction de sécurité en option

- Authentification bitstream asymétrique utilisant RSA-4096

- Cryptage/déchiffrement Bitstream à l’aide d’AES-GCM

- Prise en charge de qualité automobile avec qualification AEC-Q100

- Paquets

- FPGA 19 x 19 mm à 529 billes avec pas de 0,8 mm

- FPGA 35 x 35 mm à 1 156 billes avec pas de 1,0 mm (à venir)

- Processus de fabrication – TSMC 16 nm

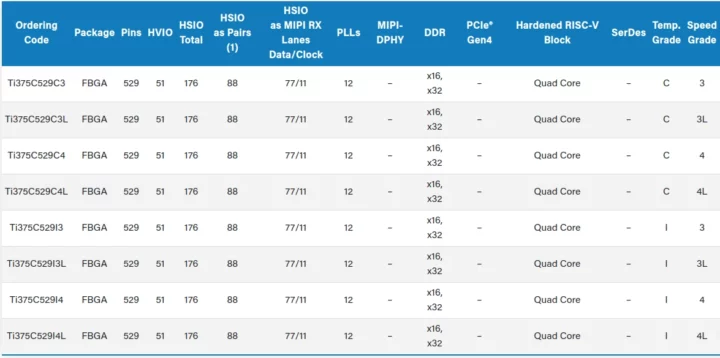

À l’heure actuelle, huit SKU FBGA à 529 billes sont disponibles avec différentes plages de température (commerciale ou industrielle) et niveaux de vitesse. Je n’ai trouvé aucune information sur les appareils FBGA à 1 156 billes, donc je suppose qu’ils pourraient arriver plus tard.

Le Ti375 est le FPGA Titanium le plus puissant d’Efinix à ce jour, bien que les FPGA Ti550, Ti750 et Ti1000 soient en préparation avec jusqu’à environ un million d’éléments logiques et l’introduction d’émetteurs-récepteurs de 25,8 Gbit/s.

Tous les FPGA Efinix, y compris le nouveau Titanium Ti375, sont pris en charge par le logiciel Efinity (compilateur RTL vers bitstream) disponible pour Windows 10/11 64 bits et Linux (Ubuntu/Red Hat Enterprise). Le bloc RISC-V du FPGA est basé sur le noyau logiciel Sapphire de la société qui peut exécuter du code nu, RTOS ou Linux. Efinix fournit une arborescence externe Buildroot personnalisée BR2-Efinix pour créer Linux avec des fichiers de configuration OpenSBI, U-boot, Linux et Buildroot ainsi que des correctifs. Vous trouverez le code et les instructions pour démarrer sur GitHub.

Il n’existe actuellement aucune information publique sur une carte d’évaluation pour le Titanium Ti375. Les applications potentielles incluent les cartes PCIe, les répéteurs RF et les unités radio, le MIMO à petites cellules/massif, les modems câble, la vision industrielle, l’automobile, les équipements et la diffusion audiovisuels, l’imagerie médicale et les ponts vidéo.

Je n’ai pas trouvé d’informations sur les prix et la disponibilité, mais Efinix s’engage à prendre en charge la famille de FPGA Titanium dans les conceptions des clients jusqu’en 2037 au moins. Des informations supplémentaires peuvent être trouvées sur la page du produit.

Retrouvez l’histoire de Raspberry Pi dans cette vidéo :