Un Loquet SR est un élément de mémoire de base dans l’électronique numérique qui stocke les données binaires à l’aide des entrées SET et réinitialise. Ce didacticiel SR Latch couvre la table de vérité, la mise en œuvre du circuit et le principe de travail des variantes de verrouillage SR de base, fermées et chronométrées.

Initialement, après l’introduction de transistors, les ingénieurs ont construit des circuits de verrouillage simples à l’aide de transistors. Après plusieurs étapes de l’évolution, les verrous dédiés ont été construits en utilisant des portes logiques comme la porte NAND et NOR GATE. Ces verrous ont été utilisés pour stocker des données, essentiellement des données binaires. Les principaux types de verrouillage incluent Latch Sr, D Latch, JK Latch et T Latch. Dans cet article, nous allons jeter un œil brièvement Loquet SRavec son Latch SR fermé et Latch SR chronométré versions.

Qu’est-ce qu’un verrou SR?

Le Loquet SRégalement connu sous le nom de Verrouillage de réinitialisationest un circuit de mémoire numérique fondamental qui stocke un bit de données binaires à l’aide de deux entrées, à savoir définir (s) et réinitialiser (R). Lorsque le réglage est activé, le verrou sortira «1» (haut), et lorsque la réinitialisation est activée, il sortira «0» (bas). La valeur stockée reste stable même après la suppression des entrées, ce qui en fait un élément de mémoire de base. Ce verrou peut être construit en utilisant ni les portes ni ou nand, la différence clé étant que la mise en œuvre de NAND utilise des entrées inversées (faibles actifs) par rapport aux portes ni aux portes.

Note: Si un circuit de verrouillage, tel qu’un verrou SR est déclenché par le bord à l’aide d’une impulsion d’horloge, il devient une bascule. Ainsi, idéalement, les verrous et les tongs sont deux choses différentes et ne doivent pas être confus pour la même chose. Dans notre cas, si le verrou SR reçoit une impulsion d’horloge, il devient un verrou SR chronométré, qui est également appelé une bascule SR. Si vous êtes complètement nouveau dans les tongs et les verrous, consultez notre tutoriel sur les bases de tongs dans l’électronique numérique.

Pour résumer, les entrées et les sorties du verrou SR sont,

- Ensemble [S]-Saisir

- Réinitialiser [R]- Saisir

- Q – Sortie

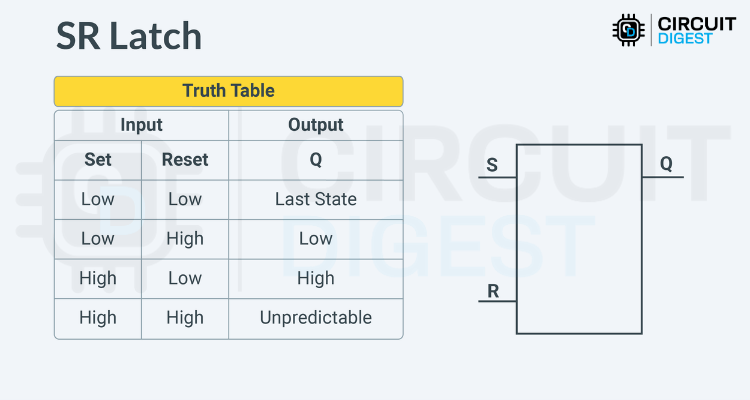

Parfois, vous pouvez également voir un Q̅, qui n’est rien d’autre qu’une sortie inversée de Q. Dans l’image ci-dessous, vous pouvez voir le symbole et un simple Table de vérité Sr Latch. À partir du tableau, vous pouvez remarquer que la logique est simple car c’est un élément de mémoire.

Il y a quatre états logiques possibles pour ce verrou:

- Lorsque les deux entrées sont FAIBLEla sortie reste inchangée. Initialement, la sortie ne sera pas définie (aléatoire), mais après toute autre condition appliquée, le «les deux bas»L’état conservera la dernière sortie.

- Lorsque le jeu est FAIBLE et la réinitialisation est HAUTla sortie q va à l’état de réinitialisation, qui est FAIBLE.

- Lorsque le jeu est HAUT et la réinitialisation est FAIBLEla sortie Q entre dans l’état défini, qui est HAUT.

- Dans le rare cas où les deux et réinitialisent HAUTla sortie Q devient instable en raison de la condition de course. Par conséquent, cet état est considéré comme invalide.

Ci-dessous, vous pouvez voir une simulation de travail d’un verrou SR simple fabriqué à l’aide de portes NAND, construite à l’aide de Proteus. Vous pouvez remarquer comment les valeurs de sortie Q et Q̅ changent en fonction des valeurs Inpput S et R.

Actuellement, jetons un coup d’œil aux versions fermées et chronométrées du verrou SR.

Latch SR fermé

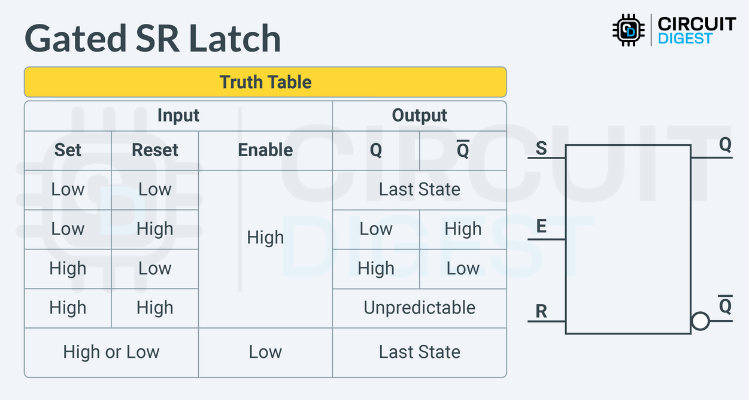

Pour la plupart, le verrou SR Gates est similaire au verrou SR standard. La seule différence est l’ajout d’une entrée supplémentaire, connue sous le nom d’activation. Ci-dessous, vous pouvez voir le Latch SR fermé Table et symbole de vérité pour une meilleure compréhension.

Il ressemble assez au verrou SRY SR. L’entrée Activer nous permet d’activer ou de désactiver le verrou, fournissant plus de contrôle par rapport à la version de base. Ci-dessous est un Verrou SR fermé construit à l’aide de portes logiques NAND Dans Proteus. Cette simulation vous aidera à comprendre clairement le concept.

La logique ici est généralement la même qu’un verrou SR standard, le seul ajout étant l’entrée Activer.

- Si l’entrée Activer est HAUT, Le verrou SR fermé fonctionne comme prévu.

- Si l’entrée Activer est FAIBLEquelles que soient les entrées S et R, la sortie reste inchangée – en d’autres termes, l’état précédent est maintenu.

Latch SR chronométré

Le Latch SR chronométré, également connu sous le nom de Tong SR, est très similaire au verrou SR fermé, sauf que l’entrée d’activation est remplacée par une entrée d’horloge. Au lieu d’une ligne d’activation stable, la sortie dépend désormais du bord montant ou descendant du signal d’horloge. C’est ce qu’on appelle le comportement déclenché par le bord.

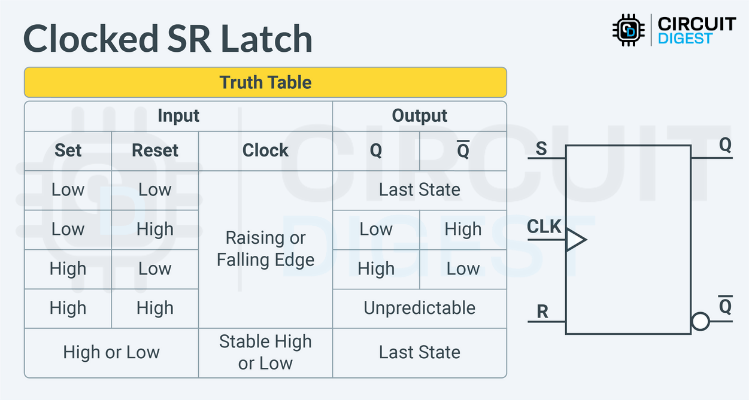

Ci-dessous, vous pouvez voir le symbole et la table de vérité Sr Latch pour une meilleure compréhension du concept.

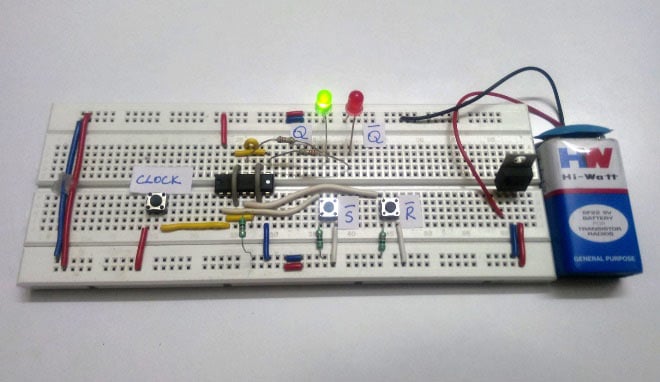

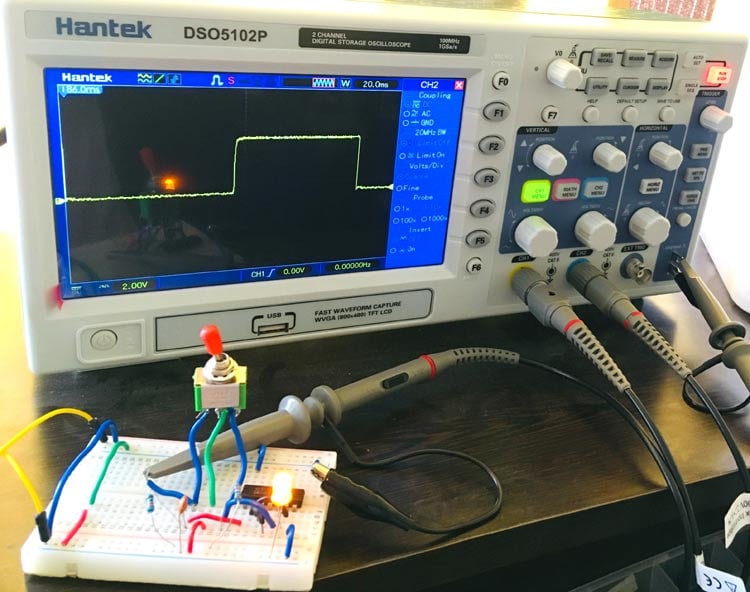

Alors, ceci Sr Latch est essentiellement un bascule SR. Pour en savoir plus à ce sujet, vous pouvez consulter l’article de bascule dans l’électronique numérique pour des informations supplémentaires et des démonstrations pratiques. Vous pouvez également afficher le résultat de la simulation en utilisant Proteus dans l’image de simulation ci-dessous.

Comme mentionné précédemment, le Latch SR chronométré est un dispositif déclenché par le bord, ce qui le rend plus fiable pour les opérations chronométrées dans des circuits séquentiels. La logique de travail est légèrement différente de celle d’un circuit de verrouillage ordinaire.

Pour rester simple, voici comment cela fonctionne:

- Aucun changement (s = r = 0): la bascule conserve son état précédent.

- Set (s = 1, r = 0): la sortie q devient «1» (set).

- Réinitialiser (s = 0, r = 1): la sortie q devient ‘0’ (réinitialiser).

- Invalide (s = r = 1): les deux sorties (q et q̅) peuvent devenir «1», conduisant à l’instabilité. Cette condition est généralement évitée dans les conceptions pratiques.

Toutes ces transitions se produisent uniquement sur le bord d’horloge positif ou négatif, selon les composants spécifiques utilisés dans le circuit.

Ce didacticiel SR Latch a couvert le principe de travail fondamental, la table de vérité et les diagrammes de circuits de verrouillage SR de base, de verrouillage SR fermé et d’implémentations de verrous SR. Comprendre ces blocs de construction de logique numérique est essentiel pour la conception de circuits séquentiels et les applications de mémoire en électronique. Si vous avez des questions, laissez-les dans les sections de commentaires au bas de cette page, et nous serons heureux d’y répondre. Vous pouvez également rejoindre notre communauté ou nos forums pour commencer une discussion.

Tutoriels similaires sur les tongs SR

Retrouvez l’histoire de Raspberry Pi dans cette vidéo :

-

Verrou électronique 12 V avec mécanisme de déclenchement solénoïde, 27 mm x 15 mm x 17 mm, loquet de porte incliné pour armoires et coffres-forts

-

Serrure électronique pour armoire, tiroir, casier en bois, serrure à capteur électronique, verrou pour armoire