Fondée il y a environ trois ans, Akeana vient de lancer et d’annoncer officiellement trois gammes de processeurs RISC-V 32 bits et 64 bits et IP SoC avec la série Akeana 100 pour les microcontrôleurs 32 bits, la série Akeana 1000 pour les processeurs 64 bits avec MMU et la série Akeana 5000 avec des performances monothread beaucoup plus élevées et conçues pour les ordinateurs portables, les centres de données et l’infrastructure cloud.

La société a également présenté Scalable Coherent Interconnect, Interrupt Controller et IOMMU IP pour la création de sous-systèmes de calcul basés sur les cœurs RISC-V susmentionnés, ainsi que les cœurs Vector RISC-V ciblés par l’IA et l’IP de calcul matriciel. L’équipe de conception aurait déjà travaillé sur les puces de serveur ThunderX2 de Marvell.

Série Akeana 100

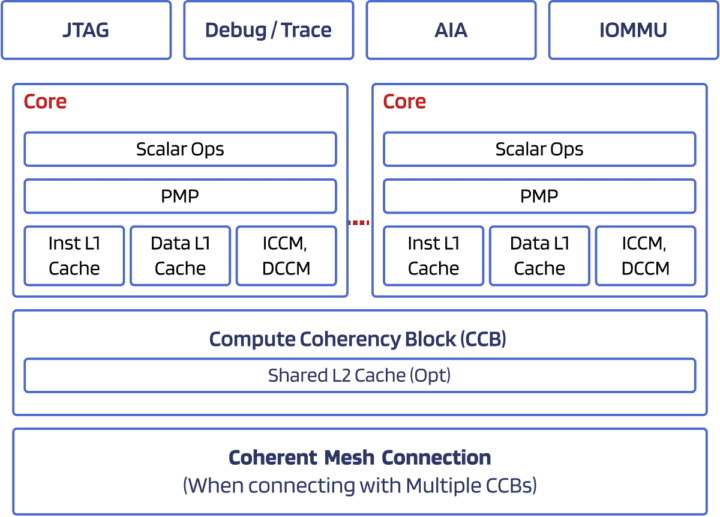

La série Akeana 100 est une gamme de processeurs hautement configurables avec des cœurs RISC-V 32 bits qui prennent en charge des applications allant des microcontrôleurs intégrés aux passerelles périphériques, en passant par les appareils informatiques personnels.

Quatre cœurs Akeana 100 RISC-V sont disponibles

- Akeana 110 pour microcontrôleurs à surface et puissance limitées

- Cache I L1 : 8 Ko/cœur

- Jeu d’instructions RV32IMAC_Zicsr_Zifencei_Zicbo

- Plage d’adresses physiques jusqu’à 32 bits

- Pipeline à 4 étages, dans l’ordre

- Problème d’instruction à largeur unique

- ICCM : 16 Ko/cœur

- DCCM : 16 Ko/cœur

- Akeana 120, 130, 140

- Caractéristiques communes

- Cache I L1 : 16 Ko/cœur

- Jeu d’instructions RV32IMAC_Zicsr_Zifencei_Zicbo

- Plage d’adresses physiques jusqu’à 32 bits

- Protection de la mémoire physique (PMP) avec 8 entrées

- Akeana 120 pour microcontrôleurs à surface et puissance limitées

- Pipeline en 5 étapes, dans l’ordre

- Problème d’instruction à largeur unique

- ICCM : 64 Ko/cœur

- DCCM : 64 Ko/cœur

- Akeana 130 pour microcontrôleurs

- Pipeline en 9 étapes, dans l’ordre

- Problème de double instruction

- ICCM : 64 Ko/cœur

- DCCM : 64 Ko/cœur

- Prédicteur de branche

- ALU secondaire pour des performances améliorées

- Akeana 140 pour des microcontrôleurs aux performances améliorées

- Pipeline en 9 étapes, dans l’ordre

- Problème de double instruction

- Cache D L1 : 16 Ko/cœur

- ICCM : 512 Ko/cœur

- DCCM : 512 Ko/cœur

- Prédicteur de branche

- ALU secondaire pour des performances améliorées

- Caractéristiques communes

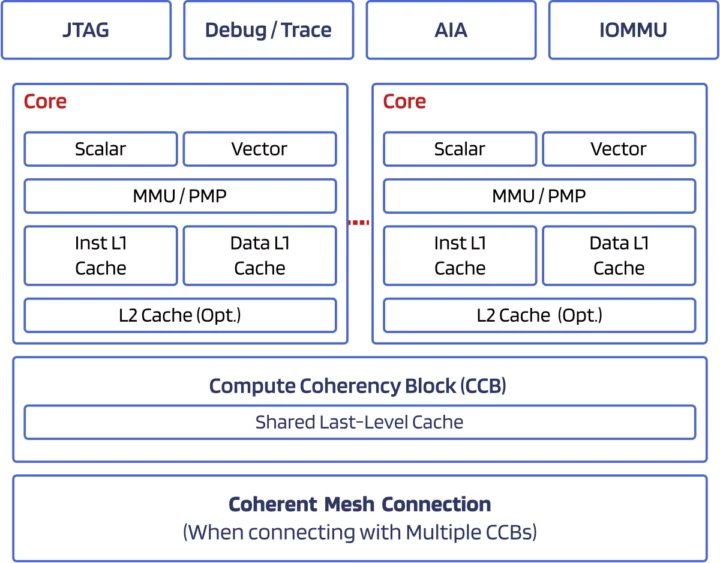

Série Akeana 1000

La série Akeana 1000 est une gamme de processeurs qui comprend des cœurs RISC-V 64 bits et une MMU pour prendre en charge les systèmes d’exploitation riches tout en maintenant une faible consommation et en nécessitant une faible surface de matrice. Ces processeurs prennent en charge les pipelines dans l’ordre ou dans le désordre, le multithreading, l’extension vectorielle, l’extension d’hyperviseur et d’autres extensions qui font partie des profils RISC-V récents et à venir (par exemple RVA23), ainsi que des extensions de calcul IA en option.

Trois cœurs RISC-V Akeana 1000 sont actuellement proposés :

- Caractéristiques communes

- Jeu d’instructions RV64GCB_Zicbo

- Profil RVA22 RISC-V complet

- Virgule flottante simple et double précision

- Mode utilisateur

- Mode superviseur

- Plage d’adresses virtuelles de 48 bits

- Plage d’adresses physiques de 39 bits

- Évolutif vers des clusters multi-cœurs entièrement cohérents

- Prise en charge de l’ECC

- AXI/ACE (512 bits)

- Protection de la mémoire physique (PMP) avec 16 entrées MU

- Akeana 1100 pour microcontrôleurs haut de gamme

- Pipeline en 9 étapes, dans l’ordre

- Envoi d’instructions doubles

- Cache I L1 : 16 Ko/cœur

- Cache D L1 : 16 Ko/cœur

- MMU avec 256 entrées, TLB 4 voies

- Akeana 1200 pour les SoC de passerelle Edge

- Pipeline en 9 étapes, dans l’ordre

- Envoi d’instructions à 3 voies

- ALU secondaire dans le pipeline

- Cache I L1 : 32 Ko/cœur

- Cache D L1 : 32 Ko/cœur

- MMU avec 256 entrées, TLB 4 voies

- Akeana 1300 pour les SoC de passerelle Edge ou comme « petit » cœur dans les configurations Big/Little avec les cœurs de la série Akeana 5000

- Pipeline à 12 étages, hors service

- Envoi d’instructions à 4 voies

- Cache I L1 : 32 Ko/cœur

- Cache D L1 : 32 Ko/cœur

- Cache L2 : 256 Ko

- MMU avec 512 entrées, TLB 4 voies

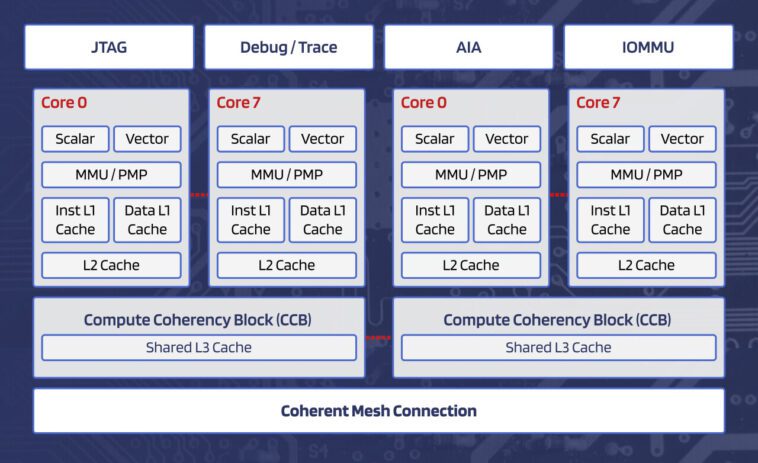

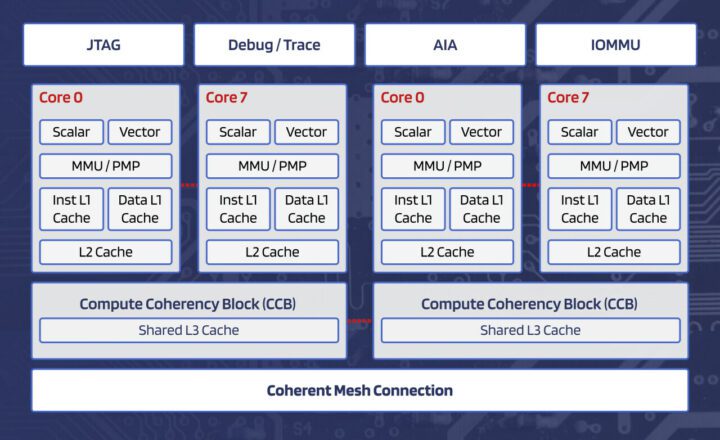

Série Akeana 5000

La série Akeana 5000 est une gamme de processeurs RISC-V hautes performances qui, selon la société, surpassent « les concurrents établis et l’écosystème RISC-V ». Cette gamme fournit des cœurs RISC-V 64 bits optimisés pour les applications exigeantes des appareils de nouvelle génération, des ordinateurs portables, des centres de données et des infrastructures cloud. Ces processeurs sont compatibles avec la série Akeana 1000 mais avec des performances monothread bien supérieures.

Trois cœurs RISC-V de la série Akeana 5000 ont été conçus

- Caractéristiques communes

- RV64GCVBK_Zicbo + jeu d’instructions USH

- Profil RVA23 RISC-V complet

- Virgule flottante simple et double précision

- Mode utilisateur

- Mode superviseur

- Extension de l’hyperviseur

- Extension vectorielle (128 bits)

- Extension de cryptographie vectorielle

- Pipeline à 12 étages, hors service

- Plage d’adresses virtuelles de 48 bits

- Cache L2 de 256 Ko

- Évolutif vers des clusters multi-cœurs entièrement cohérents

- Prise en charge de l’ECC

- AXI/ACE (512 bits)

- Protection de la mémoire physique (PMP) avec 16 entrées

- MMU

- L’Akeana 5100 sera utilisé comme « gros » cœur dans les configurations Big/Little avec les petits cœurs de la série Akeana 1000

- Envoi d’instructions à 4 voies

- Cache I L1 : 32 Ko/cœur

- Cache D L1 : 32 Ko/cœur

- Espace d’adressage physique de 33 bits

- MMU avec 512 entrées, TLB 4 voies

- L’Akeana 5200 sera utilisé dans les SoC pour ordinateurs portables comme « gros » cœur dans les configurations Big/Little avec les petits cœurs de la série Akeana 1000

- Envoi d’instructions à 6 voies

- Cache I L1 : 32 Ko/cœur

- Cache D L1 : 32 Ko/cœur

- Préchargeur de cache L2

- Espace d’adressage physique de 39 bits

- MMU avec 1024 entrées, TLB 4 voies

- Akeana 5300 – Un cœur de calcul pour centre de données/infrastructure

- Envoi d’instructions à 8 voies

- Cache I L1 : 64 Ko/cœur

- Cache D L1 : 64 Ko/cœur

- Préchargeur de cache L2

- Espace d’adressage physique de 39 bits

- MMU avec 2048 entrées, TLB 8 voies

Autres blocs IP et logiciels

La société a également introduit des « blocs IP de système de processeur » nécessaires à la conception de SoC, notamment un cache de cluster cohérent, une MMU d’E/S et des IP de contrôleur d’interruption. Akeana fournit également des IP Scalable Mesh et Coherence Hub (compatibles avec AMBA CHI) pour créer de grands sous-systèmes de calcul cohérents pour les centres de données et d’autres cas d’utilisation. Enfin, un moteur de calcul AI Matrix conçu pour décharger les opérations de multiplication de matrice pour l’accélération de l’IA est également disponible.

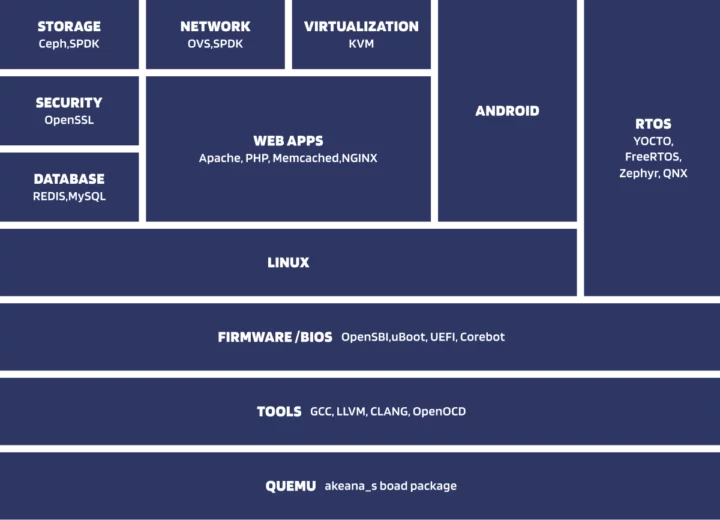

Nous avons des informations limitées sur le logiciel, mais Akeana fournit un SDK avec :

Nous pouvons voir qu’Android et Linux sont pris en charge pour les processeurs d’application, et FreeRTOS, Zephyr et QNX pour les microcontrôleurs.

Des informations complémentaires peuvent être trouvées sur le site Web de la société et dans l’annonce.

Merci à TLS pour l’information.

Retrouvez l’histoire de Raspberry Pi dans cette vidéo :