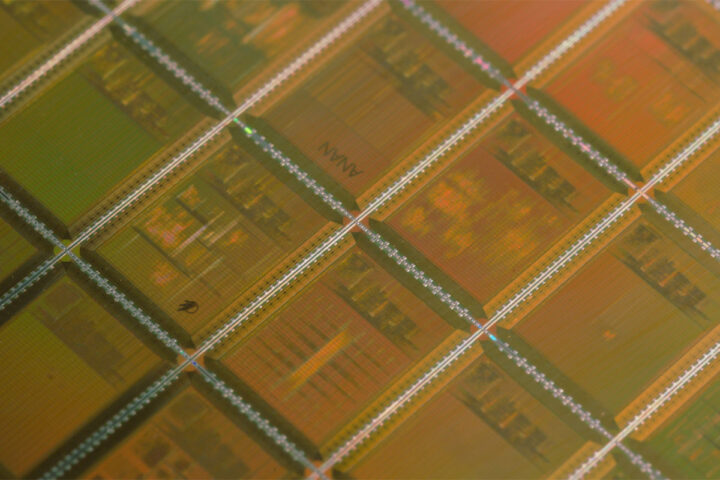

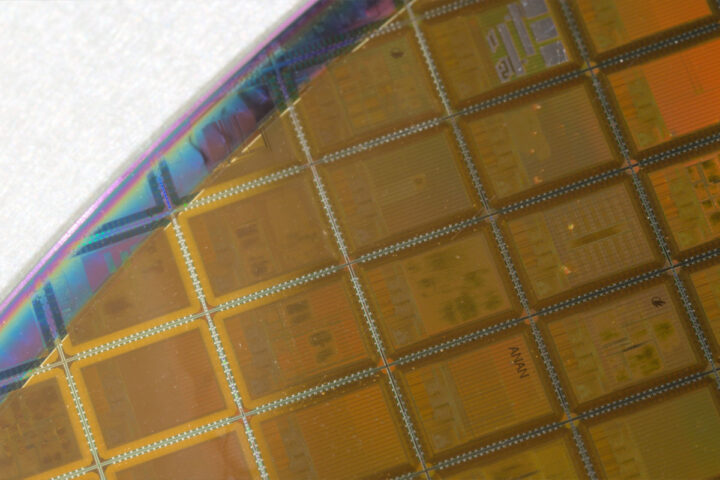

Selon cnx-software, Wafer.space a récemment introduit sa première fabrication en silicium regroupé sur la plateforme Crowd Supply, connue sous le nom de GF180MCU Run 1. Cette initiative est une véritable opportunité pour les concepteurs, les ingénieurs et les entreprises, qui peuvent désormais créer jusqu’à **1 000 ASICS** personnalisés grâce à une technologie de processus de signal mixte de **180 nm** développée par GlobalFoundries.

3,88 × 5,07 mm pour 1000 ASICS : optez pour la personnalisation

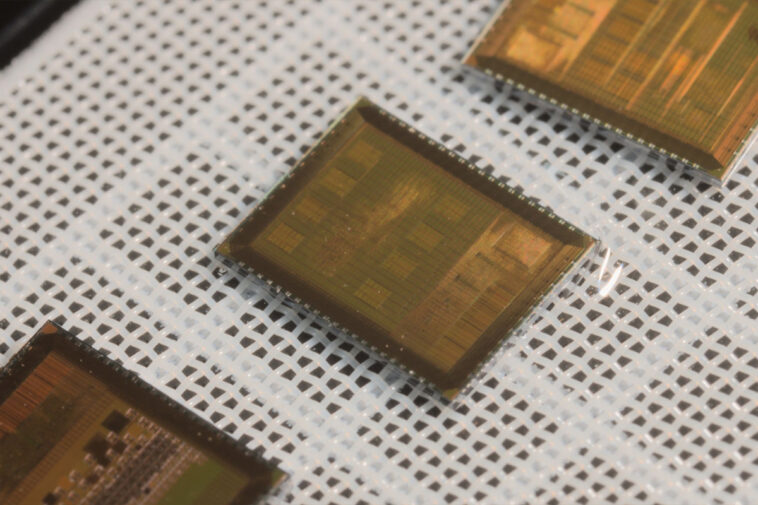

Chaque emplacement sur la tranche offre une zone de matrice standardisé de **3,88 × 5,07 mm** (19,67 mm²), disponible en **1 000 exemplaires**. Les utilisateurs peuvent choisir entre des matrices nues ou des options d’emballage de type bord. La technologie GF180MCU prend en charge jusqu’à **5 couches métalliques**, ainsi que des composants comme des condensateurs MIM d’environ **2,0 ff/µm²**, des résistances poly et polyviennes, ainsi que des dispositifs MOS standard-VT. Tout en permettant aux utilisateurs de gérer leurs propres configurations d’anneau de plaquettes, d’ESD et de dispositions d’E/S, Wafer.space s’occupe à son tour de la fabrication, des déshabillages et de l’expédition, toutes réalisées depuis Singapour. Les conceptions peuvent être soit ouvertes, soit fermées, et les utilisateurs ont également la possibilité de demander des plaques complètes pour des tests ou des collectes avancées.

Génération de puces personnalisées : une vérification simplifiée et un emballage efficace

Les utilisateurs soumettent leurs conceptions à Wafer.space sous le format de fichier GDSII, le standard courant pour les dispositions de puces. Wafer.space effectue une vérification automatique de ces fichiers pour s’assurer de leur faisabilité en production. Les concepteurs peuvent utiliser des outils open-source tels que **Librelane**, **Magic**, **Klayout**, **Xschem** et **Spice**, ou faire appel à un logiciel EDA commercial pour leurs créations.

En outre, Wafer.space propose un service d’emballage optionnel permettant de monter les puces directement sur un circuit imprimé via des modèles prêts à l’emploi. La société collabore également avec des partenaires tels que **JLCPCB**, **PCBWAY** et **Studio** pour faciliter l’assemblage et la liaison PCBA pour des analyses approfondies. Pour les recherches avancées, des plaquettes inductives complètes sont mises à disposition pour des applications MEMS, des capteurs et des nanofluidiques. Wafer.space offre également des ressources pédagogiques et des forums Discord pour aider les utilisateurs dans la conception et les vérifications finales de leurs travaux.

7 000 $ pour 1000 matrices : un investissement stratégique

Le coût pour chaque créneau de l’exécution **GF180MCU 1** est de **7 000 $** pour **1 000 matrices nues**, ou de **8 500 $** en incluant des options d’emballage de type collision et de fil à panneaux, tels que mentionnés dans la campagne. Wafer.space met à disposition des guides et une communauté en ligne pour accompagner les utilisateurs dans leur cheminement de conception, vérification et validation des conceptions finales.

La campagne de financement participatif pour **GF180MCU Run 1** prendra fin le **28 novembre 2025**, avec une date limite pour la soumission des conceptions fixée au **3 décembre 2025**. La fabrication et l’emballage seront réalisés par GlobalFoundries à Singapour, avec des expéditions prévues pour mars 2026. Pour des informations détaillées, rendez-vous sur le site de Wafer.space, où vous trouverez également une interview en ligne avec le fondateur de l’entreprise.