L’écosystème RISC-V connaît une accélération remarquable avec l’annonce de trois processeurs haute performance lors du récent sommet RISC-V en Chine. Selon les informations rassemblées, les Ultrarisc UR-DP1000, Zhihe A210 et Spacemit K3 représentent une nouvelle génération de puces RISC-V visant à rivaliser avec les architectures établies ARM et x86 dans des domaines jusqu’alors inaccessibles. Ces processeurs marquent un tournant décisif pour l’architecture open-source, passant des applications embarquées vers les ordinateurs de bureau, serveurs edge et calcul haute performance. Avec des performances annoncées dépassant les architectures Haswell et Zen1 d’Intel/AMD sur certains benchmarks, ces puces illustrent la maturité croissante de RISC-V pour des applications exigeantes.

Ultrarisc UR-DP1000 : premier processeur desktop RISC-V avec virtualisation matérielle

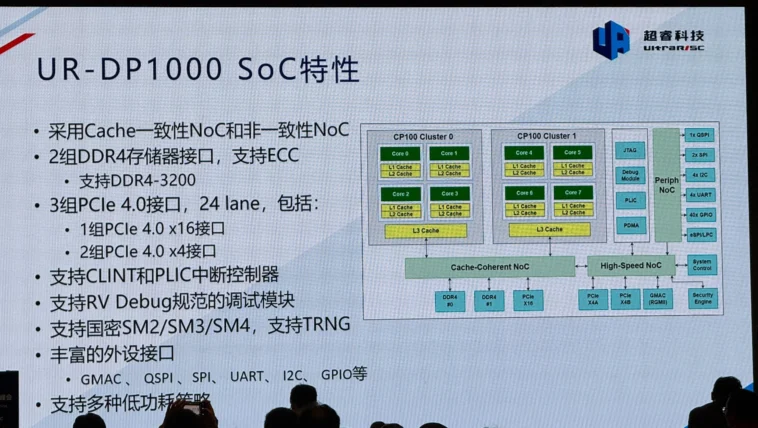

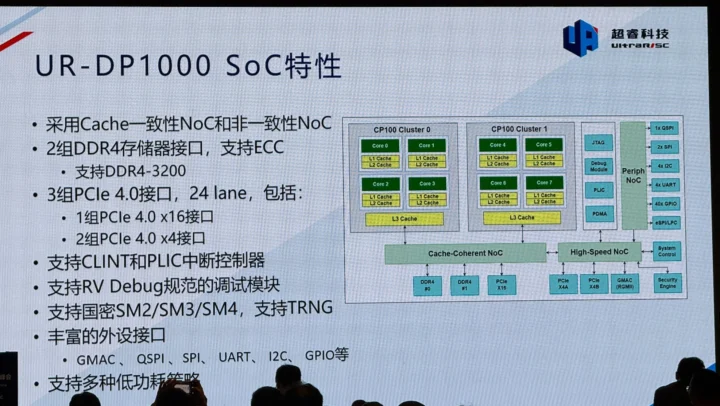

Le processeur Ultrarisc UR-DP1000 se positionne comme le plus abouti des trois avec une disponibilité prévue dès l’automne 2025 via la carte mère Titan Mini-ITX de Milk-V. Cette puce octa-core exploite 8 cœurs UR-CP100 cadencés jusqu’à 2,0 GHz dans une architecture dual-cluster avec 4 MB de cache L3 par cluster et 16 MB de cache système partagé. Le TDP de 30W la positionne pour des applications desktop exigeantes.

L’architecture UR-CP100 implémente le jeu d’instructions RV64GCBHX avec support de virtualisation matérielle via l’extension H(v1.0), fonctionnalité critique pour l’émulation et les environnements virtualisés. Les performances annoncées atteignent 10,4 SPECint2006/GHz et 12,0 SPECfp2006/GHz, dépassant les cœurs Cortex-A76 du Raspberry Pi 5 (9,9 SPECint2006/GHz).

Le principal inconvénient réside dans l’absence de l’extension vectorielle RISC-V, limitant les performances pour les applications IA et calcul scientifique comparé aux alternatives RVA23 complètes. La carte Titan propose néanmoins 24 voies PCIe 4.0, 64 GB DDR4-3200 ECC et prix accessible de 279 $ une fois disponible.

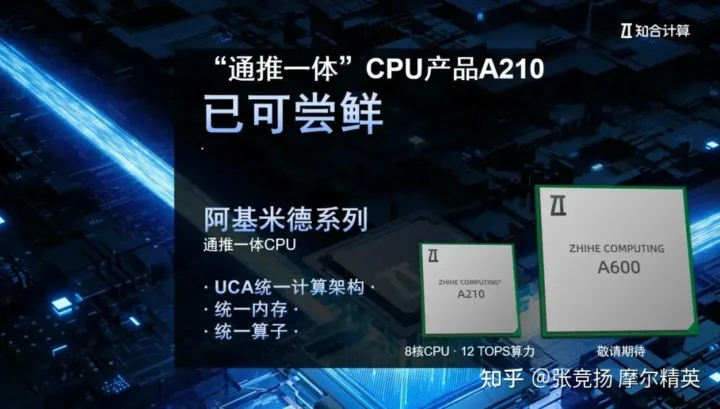

Zhihe A210 : architecture unifiée avec 12 TOPS d’accélération IA intégrée

Le processeur Zhihe A210 adopte une approche radicalement différente avec son Architecture de Calcul Unifiée (UCA) intégrant mémoire et opérateurs unifiés pour optimiser l’efficacité computationnelle. Cette puce 8 cœurs RISC-V 64-bit délivre jusqu’à 12 TOPS (INT8) de puissance IA sans NPU séparée, approche innovante pour l’inférence distribuée.

La conformité RVA23 complète avec support des 81 extensions obligatoires et optionnelles, incluant Hyperviseur, Vecteur, BF16, CFI et Sv57, positionne l’A210 comme référence technique. Le support de 123 extensions RISC-V officielles couvrant AME, AIA, CoVE, Smmtt, QoS, IOMMU et RERI illustre l’ambition serveur de cette plateforme.

Les applications cibles incluent serveurs edge, encodage/décodage vidéo, chiffrement/déchiffrement et inférence de modèles larges incluant architectures Mixture of Experts comme DeepSeek. Zhihe revendique des performances vectorielles égales ou supérieures aux instructions Intel et ARM pour certaines tâches critiques.

L’entreprise annonce fabrication et tests internes terminés avec échantillons disponibles pour développeurs, suggérant disponibilité imminente malgré l’absence de site web officiel.

Spacemit K3 : évolution des cœurs X100 vers architecture 64 cœurs

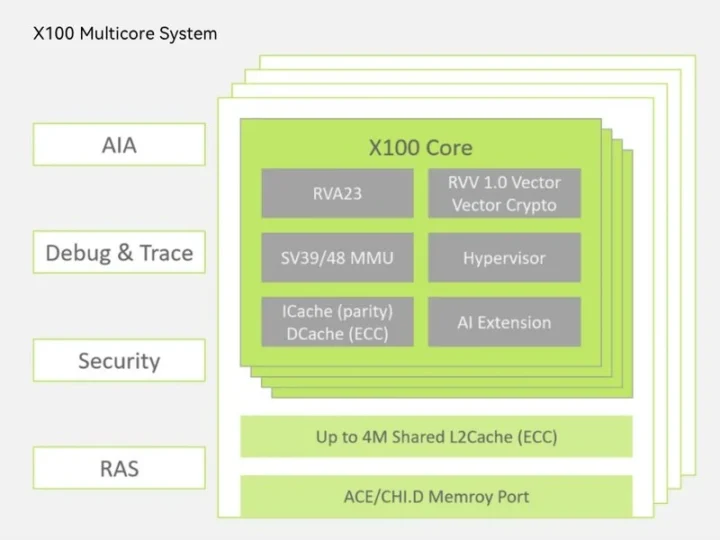

Spacemit, déjà établi dans l’écosystème RISC-V via les processeurs K1 et M1 présents dans Orange Pi R2S, Banana Pi BPI-CM6 et Muse Pi Pro, développe le K3 autour des cœurs X100 haute performance. Ces cœurs RVA23 64-bit offrent 2,5 TOPS @ INT8 par cœur avec conformité extension RISC-V IME.

L’architecture X100 implémente exécution hors-ordre 12 étages à 4 issues cadencée à 2,5 GHz en process 12nm, délivrant 9,0 SPECint2006/GHz avec compilateur LLVM Spacemit optimisé. Le support vectoriel RISC-V 1.0 avec bande passante 256-bit et extensions crypto vectorielles ciblent calcul scientifique et cryptographie.

La scalabilité architecture supporte jusqu’à 64 cœurs en configuration multi-cluster avec cohérence intra et inter-cluster, positionnant le K3 pour applications serveur exigeantes. Les fonctionnalités niveau serveur incluent support RAS, protection Meltdown/Spectre et trace d’instructions pour debugging avancé.

Spacemit exploite cette architecture dans le SOC serveur Vital Stone V100 annoncé en janvier 2025, démontrant maturité technologique pour déploiements datacenter.

Impact stratégique et perspectives 2025-2026 pour l’écosystème RISC-V

Ces trois processeurs illustrent la bifurcation stratégique de RISC-V entre approches complémentaires : Ultrarisc privilégie compatibilité desktop immédiate, Zhihe optimise serveurs edge avec IA intégrée, tandis que Spacemit vise scalabilité datacenter. Cette diversité renforce l’adaptabilité de l’architecture open-source face aux besoins variés du marché.

La transition vers RVA23 constitue un enjeu critique pour l’adoption mainstream, éliminant les recompilations constantes qui ont freiné l’écosystème logiciel. Seuls A210 et K3 offrent conformité complète, questionnant la viabilité long terme de l’UR-DP1000 malgré sa disponibilité anticipée.

Les performances annoncées dépassant Haswell et Zen1 sur certains benchmarks marquent un seuil psychologique important, démontrant que RISC-V peut rivaliser avec architectures établies plutôt que se contenter de niches spécialisées. Cette évolution pourrait catalyser adoption plus large si confirmée par silicium réel.

L’horizon 2025-2026 s’annonce décisif avec hardware disponible automne 2025 pour l’UR-DP1000 et support Linux mainline prévu Q4 2026. Les trois plateformes nécessiteront probablement optimisations logicielles substantielles avant utilisation productive, période critique pour démontrer viabilité de l’écosystème RISC-V au-delà des promesses marketing.

Retrouvez l’histoire de Raspberry Pi dans cette vidéo :

-

Obotsnoi Carte de processeur RISC V intégrée avec et fonctions de sécurité USB Carte de développement

-

Traitement des données informatiques Processeur E5 2650 V3 SR1YA 2,3 Ghz 10105 W Prise LGA 2011-3