Selon cnx-software, NXP a récemment dévoilé son processeur d’applications i.MX 952, qui fait partie de la série i.MX 95. Ce processeur est spécialement conçu pour des applications automobiles et industrielles intégrant de l’intelligence artificielle, telles que la surveillance des conducteurs, la détection d’enfants et les interfaces homme-machine (IHM) en cabine.

i.MX 952 et 500 Mpixel/s : un traitement visuel performant

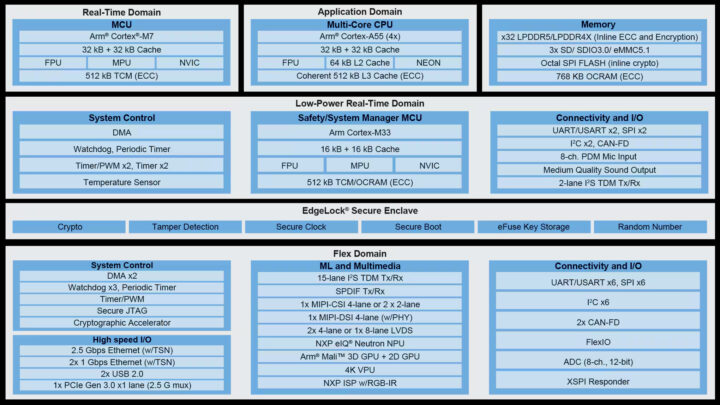

Le processeur i.MX 952 est équipé de jusqu’à quatre cœurs Arm Cortex-A55, accompagnés de cœurs de microcontrôleur Cortex-M7 et M33. Il respecte les normes ISO 26262 ASIL B et SIL2/SIL3, garantissant une sécurité robuste. L’appareil est pourvu d’un NPU eIQ Neutron, qui permet une fusion des capteurs par le biais de l’intelligence artificielle. De plus, son FAI peut atteindre une capacité de 500 Mpixel/s avec support pour les images RVB-IR. Le processeur est également le premier à intégrer une gradation locale pour une efficacité d’affichage améliorée. Pour assurer un niveau de sécurité élevé, il intègre EdgeLock Secure Enclave, qui utilise une cryptographie post-quantique, conforme aux normes ISO 21434 et IEC 62443. Il est possible de le connecter avec les SoC PF09 PMIC, PF53, Trimension UWB et IW693/AW693 Wi-Fi 6/6E de NXP, tout en restant compatible broche à broche avec les autres membres de la famille i.MX 95.

128 Mo de cache et plusieurs normes de sécurité : une plate-forme flexible

Le NXP i.MX 952 est composé de plusieurs éléments techniques essentiels. Il propose jusqu’à quatre cœurs Arm Cortex-A55, chacun étant accompagné de caches L1 de 32 Ko, L2 de 64 Ko, et L3 de 512 Ko avec ECC. De plus, il comporte un cœur temps réel Cortex-M7 et un microcontrôleur Cortex-M33 à faible consommation, renforçant l’aspect sécurité et réactivité du processeur. Le GPU 3D intégré, bien que non spécifié, est capable de gérer des APIs telles qu’OpenGL ES 3.2, Vulkan 1.2 et OpenCL 3.0.

En matière de mémoire, l’appareil prend en charge jusqu’à 32 Go de LPDDR5 à 6 000 MT/s ou LPDDR4X à 4 266 MT/s, garantissant un cryptage en ligne pour une protection accrue des données. En plus de cela, il est pourvu de plusieurs interfaces de stockage incluant trois interfaces uSDHC et un Flash SPI octal, apportant flexibilité dans les solutions de stockage.

Le schéma fonctionnel démontre que l’i.MX 952 maintient l’architecture hétérogène de l’i.MX 95 avec ses cœurs Cortex-A55, M7, et M33, ainsi que son NPU eIQ Neutron. Toutefois, il introduit des améliorations comme la gradation locale pour les écrans et l’intégration de cryptographie post-quantique au sein de l’enclave sécurisée EdgeLock. Par rapport à son prédécesseur, il réduit le nombre de cœurs de processeur de six à quatre tout en optimisant la mémoire sur puce et en offrant des options d’E/S efficaces.

La prise en charge de BSP pour Linux et Android est disponible pour les cœurs d’application Cortex-A55, tandis que FreeRTOS est utilisé pour les cœurs en temps réel et de sécurité. Le NPU intégré eIQ Neutron est compatible avec l’environnement de développement d’apprentissage automatique eIQ de NXP, facilitant l’optimisation et le déploiement des charges de travail d’IA. Les développeurs disposent également d’un SDK basé sur Yocto, et des outils de sécurité pour assurer une intégration efficace.

À ce jour, diverses cartes de développement et systèmes sur modules se basent sur le SoC i.MX 95, incluant des modèles comme l’ADLINK OSM-IMX95 et le kit d’évaluation Toradex Titan.

En préproduction, le processeur i.MX 952 voit ses spécifications encore évoluer. Pour plus d’informations, il est conseillé de consulter la page produit ou le communiqué de presse officiel.

-

Processeur Intel Xeon E5-2695 V4 2, 1 GHz (Broadwell-EP) Sockel 2011-V3 - Bo