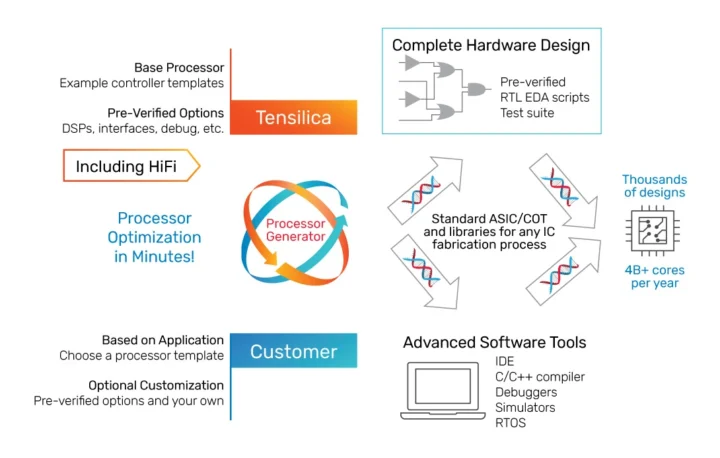

Selon cnx-software, le Tensilica HiFi iQ DSP IP représente la sixième génération de la série HiFi DSP, intégrée dans de nombreux SoC dédiés à l’audio. Cette version repose sur une architecture innovante, optimisée pour les applications d’intelligence artificielle liée à la voix, ainsi que pour des expériences audio immersives.

Performances doublées et économie d’énergie de 25 % avec Tensilica HiFi iQ DSP

Comparé à son prédécesseur, le Tensilica HiFi 5s, le DSP HiFi iQ offre des performances de calcul qui sont deux fois supérieures, avec une capacité d’IA affichant une amélioration de huit fois. En ce qui concerne l’efficacité énergétique, le nouvel DSP parvient à réduire la consommation de plus de 25 % pour de nombreuses charges de travail. Par ailleurs, quand il s’agit de plusieurs codecs audio, le HiFi iQ propose une augmentation de performances de plus de 40 %. Cadence présente cet équipement comme un processeur d’IA tout-en-un, capable de faire tourner les modèles de langage (SLM et LLM) directement au sein du DSP.

Caractéristiques impressionnantes et compatibilité avec des codecs avancés

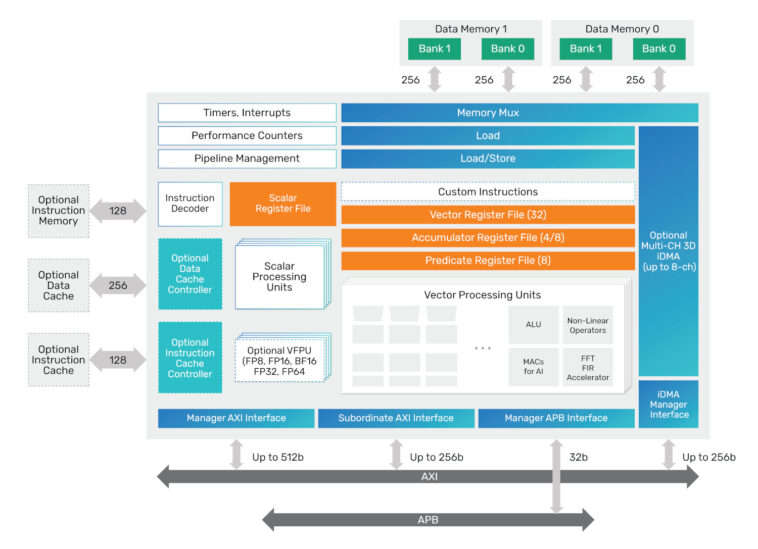

Le Tensilica HiFi iQ DSP se distingue grâce à une architecture comprenant des unités de charge au nombre de deux et cinq emplacements VLIW, permettant de gérer des opérations vectorielles de 256 bits. Le support des MAC à virgule fixe et pour l’IA, allant jusqu’à 128 16×8 et 256 16×4, sont améliorés par rapport aux modèles précédents. Les instructions pour l’IA sont également bien plus diversifiées, facilitant ainsi une programmation optimisée. De plus, la prise en charge de la virgule flottante vectorielle dans plusieurs formats tels que FP16 et FP32 offre une flexibilité accrue.

Ce DSP est capable de gérer des codecs audio avancés comme Dolby MS12, Eclipsa Audio, Opus HD, et Audio Vivid. La conception de cette architecture permet de soutenir efficacement des algorithmes pour des applications telles que la détection de mots clés, la suppression active du bruit, et la reconnaissance de la parole. L’HiFi iQ DSP est également adapté pour des SoC respectant les strictes normes de sécurité fonctionnelle ISO 26262, nécessaires dans les applications critiques.

Une interface audio multi-flux et multi-canaux améliore l’expérience audio, rendant possible la création de zones sonores 3D ou des bulles sonores. Le nouveau DSP travaille en adéquation avec les environnements Cadence NeuroWeave SDK, ainsi que TensorFlow Lite for Micro, permettant une exécution de modèles d’IA de manière fluide.

La disponibilité du Tensilica HiFi iQ DSP est prévue pour le premier trimestre 2026 pour les clients et partenaires principaux, tandis que la disponibilité générale devrait avoir lieu dans le courant du deuxième trimestre 2025. Des informations supplémentaires sont accessibles sur la page produit ainsi que dans le communiqué de presse. De plus, un tableau comparatif des différentes générations de DSP Tensilica HiFi est disponible pour évaluer les évolutions de performances.

| Caractéristiques | HiFi 1 | Hifi 3z | Chaîne Hi-Fi 4 | Hifi 5s | HiFi iQ | |

|---|---|---|---|---|---|---|

| Machines à sous VLIW | 2 | 3 | 4 | 5 | 5 | |

| SIMD | 64 bits | 64 bits | 64 bits | 128 bits | 256 bits | |

| MAC à virgule fixe | 32×32 | 1 | 2 | 4 | 8 | 16 |

| 32×16 | 2 | 4 | Jusqu’à 8 | 16 | 32 | |

| 16×16 | 4 | Jusqu’à 8 | Jusqu’à 8 | 16 | 64 | |

| MAC pour l’IA (facultatif) | 16×8 | 8 | – | – | 32 | Jusqu’à 128 |

| 8×8 | 8 | – | – | 32 | Jusqu’à 256 | |

| Accumulateur | 64 bits | 64 bits | 64/72 bits | 64/72 bits | 80 bits | |

| Instructions pour l’IA | Limité; compris | – | – | Oui; facultatif | Oui++ ; en option (amélioré par rapport à HiFi 5s) | |

| Virgule flottante vectorielle (facultatif) | PC8 | – | – | – | – | 16/32 (conversion) |

| BF16 | – | – | – | – | 16/32 (conversion) | |

| PC16 | – | – | – | 8/16 | 16/32 | |

| FP32 | 2 | 2 | 2 | 4/8 | 8/16 | |

| FP64 | 1 (scalaire) | 1 (scalaire) | 1 (scalaire) | 1 (scalaire) | 4/8 | |

| Virgule flottante complexe (avec ADDSUB) | Oui | Oui | Oui | Oui | Oui++ (amélioré) | |

| Prise en charge de la vectorisation automatique | Oui | – | – | Oui | Oui++ (amélioré par rapport à HiFi 5s) | |

| Soutien intrinsèque de l’UIT | Oui | Oui | Oui | Oui | Oui | |

| Prise en charge du tampon circulaire | 1 | 1 | 2 | 3 | 3 | |

| Prise en charge du flux binaire VLE/VLD | VLD | Oui | Oui | Oui | Oui | |

| Instructions définies par l’utilisateur (TIE) | Oui | Oui | Oui | Oui | Oui | |

Merci à TLS pour le conseil.