MIPS a dévoilé pour la première fois la série IP MIPS P8700 ainsi que les cœurs IP multiprocesseur I8500 en 2022, et la société a maintenant annoncé la disponibilité générale du cœur RISC-V 64 bits P8700. Conçu pour les systèmes avancés d’aide à la conduite (ADAS), le ML et les applications automobiles basées sur des logiciels, le système multitraitement (MPS) MIPS P8700 évolue jusqu’à 64 clusters hétérogènes de processeurs MIPS multicœurs et multithreads dans le désordre.

Architecture RISC-V du processeur RISC-V de la série P8700

Le P8700 est la première IP RISC-V de MIPS. Il implémente l’architecture du jeu d’instructions RISC-V RV64GCZba_Zbb. Il permet au MPS d’exécuter des opérations atomiques, des opérations à virgule flottante simple précision et double précision et intègre des extensions de manipulation de bits, qui rationalisent les tâches de traitement des données. Cette capacité avec des instructions compressées via l’extension RISC-VC C (RVC) permet un multithreading dans le désordre.

Clustering multithread et hétérogène dans le désordre de la série P8700

Le multithreading dans le désordre signifie simplement que le MPS traite plusieurs instructions simultanément sans suivre un ordre. Par conséquent, le MPS peut traiter simultanément même des instructions co-dépendantes, regrouper les résultats et fournir le résultat souhaité plus rapidement, réduisant ainsi la latence. MIPS affirme que le P8700 réalise jusqu’à 60 % de gains de performances par rapport à l’exécution dans l’ordre. Pendant ce temps, un pipeline de récupération d’instructions de 8 largeurs, un pipeline d’émission de 7 largeurs et un pipeline de décodage de 4 largeurs garantissent un débit élevé.

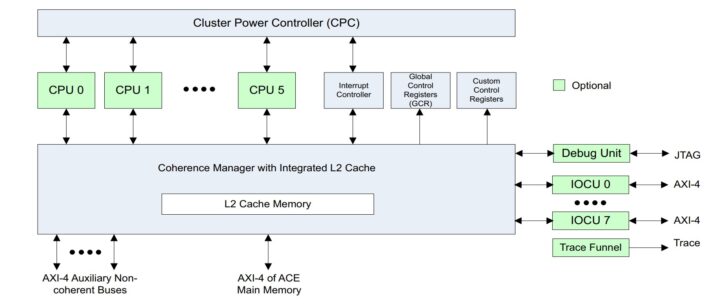

Le système multitraitement (MPS) P8700 utilise une architecture de cluster hautement évolutive et configurable, ce qui le rend adapté à diverses applications gourmandes en calcul. Chaque cluster peut héberger jusqu’à six cœurs de processeur RISC-V et huit unités de cohérence d’E/S (IOCU), avec une limite totale de huit agents par cluster. Le Coherence Manager (CM) assure la cohérence du cache à l’aide d’un protocole basé sur un répertoire, gérant à la fois les caches de niveau 1 (L1) et de niveau 2 (L2), ce dernier offrant des tailles allant jusqu’à 8 Mo. L’architecture prend en charge jusqu’à 64 clusters, évoluant jusqu’à 512 cœurs et 2 048 threads matériels (harts). La flexibilité est encore améliorée grâce à des domaines d’horloge indépendants, permettant des performances et une efficacité énergétique personnalisées pour les cœurs, le CM et les interfaces d’E/S. De plus, le Cluster Power Controller (CPC) offre une gestion dynamique de l’énergie, permettant un contrôle de l’alimentation au niveau du cœur et des ajustements d’horloge pour optimiser la consommation d’énergie.

La configurabilité est une caractéristique du P8700 MPS, avec des options permettant de faire varier le nombre de cœurs, les tailles de cache, les IOCU et les configurations de mémoire pour répondre aux besoins spécifiques des applications. Les caches L1 et L2 sont personnalisables et prennent en charge une gestion efficace de la mémoire avec des fonctionnalités telles que la protection ECC et les transferts de données cache à cache. Le système prend en charge les configurations cohérentes et non cohérentes, avec les interfaces AXI-4 et ACE pour les configurations mono-cluster et multi-cluster, respectivement. Les capacités de débogage, notamment les modes de débogage PDTrace et hybride, améliorent le développement et le dépannage. Grâce à cette architecture robuste, le P8700 MPS est bien adapté aux applications dans les domaines de l’automobile, de l’apprentissage automatique, des réseaux et des systèmes embarqués hautes performances.

MIPS P8700 sera présent dans les SoC MobileEye

Le MIPS P8700 sera intégré aux systèmes sur puces (SoC) de Mobileye conçus pour les plates-formes de conduite autonome. Mobileye a intégré des processeurs MIPS dans plusieurs générations EyeQ, de EyeQ2 à EyeQ6H et EyeQ6L, et maintenant dans sa plateforme EyeQ de nouvelle génération. Cela inclut également le très attendu Mobileye EyeQ7 et certaines générations précédentes. Le partenariat a été annoncé en 2022.

MIPS P8700 : spécifications

- Architecture du jeu d’instructions : RISC-V RV64GCZba_Zbb

- Modes privilégiés : Superviseur, Machine, Débogage

- Cœurs par cluster : jusqu’à 6

- Threads par cœur : 1 ou 2

- Évolutivité : jusqu’à 64 clusters, 512 cœurs, 2 048 threads

- Pipeline : récupération en 8 largeurs, décodage en 4 largeurs, problème en 7 largeurs

- Cache d’instructions L1 : 32 Ko ou 64 Ko

- Cache de données L1 : 32 Ko ou 64 Ko

- Cache L2 : 256 Ko à 8 Mo

- Tailles de page MMU : jusqu’à 512 Go

- IOCU par cluster : jusqu’à 8

- Chemins de données internes : 512 bits

- Prise en charge du débogage : EJTAG, trace RISC-V

- Gestion de l’alimentation : gestion de l’alimentation au niveau du cœur et du cluster

- Sécurité fonctionnelle : conforme à ASIL-B(D)

- Interface de bus système : AMBA ACE, AXI-4

MIPS a intégré la sécurité fonctionnelle et la capacité de configuration dans le MIPS P8700 MPS. Il est conforme à ASIL-B (D) pour les applications industrielles et automobiles et inclut une protection de parité et une correction d’erreur SRAM.

Le MIPS P8700 MPS IP est désormais disponible sur le marché plus large et les livraisons avec les lancements OEM commenceront bientôt. Le site Web de MIPS contient des informations plus utiles, notamment la fiche technique et un guide du programmeur.

Retrouvez l’histoire de Raspberry Pi dans cette vidéo :