Lattice Semiconductor a récemment présenté la famille de FPGA MachXO5D-NX, qui intègre une root de confiance matérielle (RoT) dans les FPGA basse consommation. Cette solution répond aux défis de sécurité en combinant la mémoire Flash sur puce et le cryptage matériel pour minimiser les risques de capture de code pendant le temps de chargement.

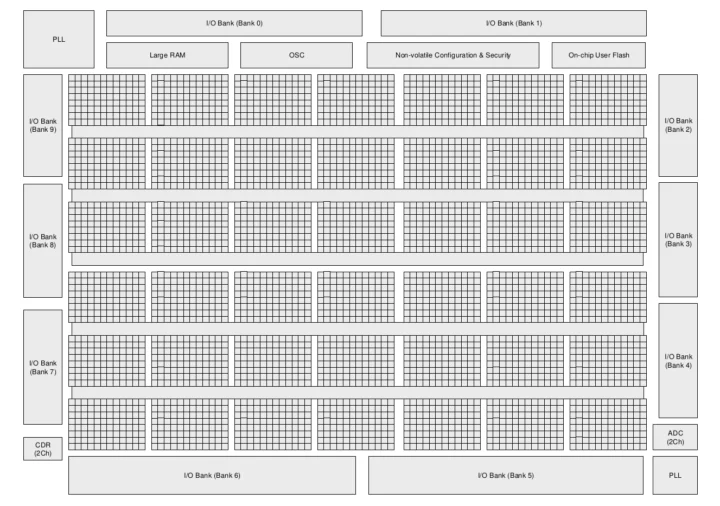

La famille MachXO5D-NX comprend trois variantes avec un nombre de cellules logiques de 27 000 (FMXO5-25), 53 000 (LFMXO5-55T) et 96 000 (LFMXO5-100T). Ces FPGA disposent d’un cryptage matériel intégré, d’un moteur cryptographique prenant en charge AES-256, ECDSA-384/521, SHA2-256/384/512 et RSA 3072/4096, ainsi que d’une identité secrète unique (USID) pour la protection de l’identité de l’appareil. Construits sur un processus FD-SOI (Fully Depleted Silicon On Insulator) de 28 nm, ces FPGA réduisent la consommation d’énergie de 75 % et réduisent les taux d’erreurs logicielles de 100 fois (comme le mentionne la société). Ils prennent en charge des interfaces telles que MIPI D-PHY (CSI-2, DSI), LVDS, Gigabit Ethernet et PCIe, ce qui les rend adaptés aux applications de périphérie sécurisées.

Spécifications de la famille FPGA Lattice MachXO5D-NX

- FPGA – Famille de FPGA Lattice Semi MachXO5D-NX (27k (FMXO5-25), 53k (LFMXO5-55T) et 96k (LFMXO5-100T))

- Logique programmable – 27 000 à 96 000 cellules logiques, 20 à 156 multiplicateurs

- Mémoire – 1,9 Mo à 7,3 Mo de mémoire intégrée, prise en charge DDR3/DDR3L/LPDDR4

- Interfaces – MIPI D-PHY, LVDS, SLVS, SGMII, PCIe Gen1/2, Ethernet

- E/S – 200-300 E/S programmables, hautes performances (1,8 V) et large plage (3,3 V)

- Fonctionnalités analogiques Double ADC (1 MSPS, SAR 12 bits), trois comparateurs à temps continu

- Fonctionnalités de sécurité – Cryptage du flux binaire (AES-256), authentification (ECDSA), démarrage sécurisé

- Fonctionnalités supplémentaires – Récupération des données d’horloge (CDR), blocs sysDSP avec décalage dynamique pour AI/ML, sysMEM EBR, atténuation des erreurs logicielles, double ADC, double DAC

- Gestion de l’alimentation – Modes basse consommation et hautes performances

- Dimensions – 17 x 17 mm

Veuillez noter qu’il s’agit d’un aperçu résumé des capacités de la famille FPGA MachXO5-NX. Pour plus d’informations, vous pouvez consulter la fiche technique de la famille MachXO5-NX sur le site Web de Lattice Semiconductor.

Les FPGA MachXO5-NX permettent des applications d’IA de pointe et de calcul intensif avec des multiplicateurs et des cellules DSP. Le FPGA est également doté d’interfaces MIPI, LVDS, Ethernet, PCIe et DDR. La mémoire Flash intégrée prend en charge le multi-boot et le stockage utilisateur. De plus, les puces sont compatibles avec la suite de conception Lattice Radiant et utilisent des modules IP pré-conçus.

Ce FPGA est également doté d’un moteur cryptographique basé sur le matériel avec des normes de cryptage avancées (AES), d’un véritable générateur de nombres aléatoires et d’une identité secrète unique pour une sécurité renforcée. Les appareils sont crypto-agiles, ce qui signifie qu’ils peuvent basculer entre plusieurs algorithmes ou méthodologies cryptographiques. De plus, ils prennent en charge les algorithmes de sécurité nationale commerciale (CNSA) spécifiés pour les algorithmes de flux binaire et cryptographiques tels que AES-256 et SHA2-512. En intégrant des fonctionnalités de sécurité dans le matériel, aucune structure FPGA n’a besoin d’être dédiée à la sécurité, ce qui garantit une utilisation efficace des ressources.

Le MachXO5-NX intègre une architecture en couches FD-SOI qui réduit le courant de fuite, ce qui se traduit par une consommation d’énergie inférieure de 75 % et une réduction de 100 fois des erreurs logicielles. Cela signifie qu’il peut être utilisé dans des environnements électriquement bruyants et sujets aux radiations.

Un autre problème que cette puce résout est le risque de capture de code, une capture de code est effectuée après avoir piraté une puce. Le piratage est un processus par lequel vous alimentez la puce avec une impulsion électrique ou une fluctuation de tension qui provoque un dysfonctionnement temporaire de la puce, ce qui permet au pirate de contourner les indicateurs de sécurité et de configuration, puis un code malveillant peut être exécuté ou un code peut être copié à partir de la mémoire.

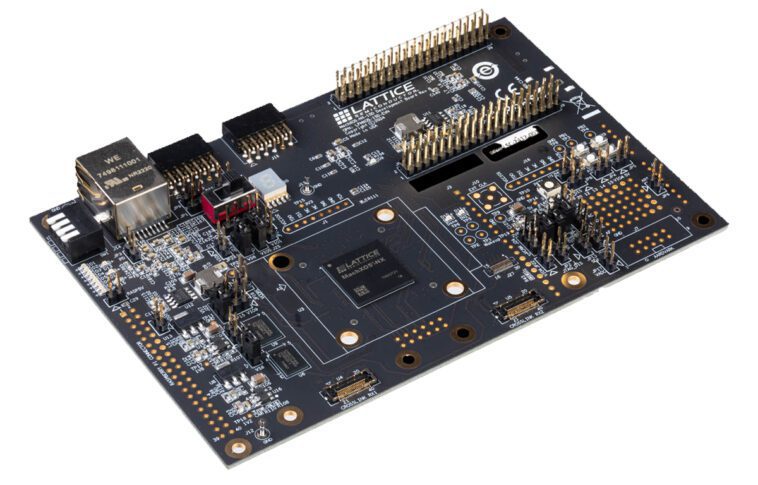

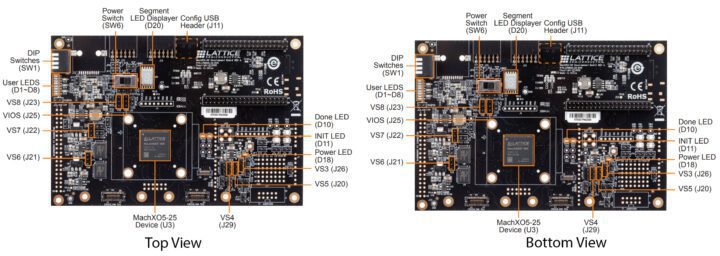

La société propose également la carte de développement MachXO5-NX construite autour du FPGA MachXO5-NX-25 et dotée d’une gamme de fonctionnalités pour un contrôle et une gestion système sécurisés. Elle offre des options d’E/S flexibles, notamment SGMII et ADC, et pour la rendre plus intéressante, elle est compatible avec divers connecteurs d’extension comme Arduino, Raspberry Pi et FX12. De plus, elle prend en charge plusieurs modes de configuration (JTAG, I2C/I3C, SPI), la programmation embarquée via USB et comprend des composants tels que HyperRAM, des LED, des commutateurs et des boutons à des fins de démonstration et de prototypage. La carte est conçue pour simplifier le processus de développement.

Je n’ai pas réussi à trouver de lien d’achat pour le circuit intégré FPGA lui-même, mais j’ai trouvé une liste Digikey où la carte de développement peut être achetée pour 199 $. Vous trouverez plus d’informations sur la puce sur la page produit de l’entreprise ou dans le communiqué de presse.

Retrouvez l’histoire de Raspberry Pi dans cette vidéo :