Le projet « Analyseur logique intégré » (ILA) de Cologne Chip est une implémentation open source Verilog d’un analyseur logique fonctionnant sur le FPGA GameMate A1 de la société et conçu pour capturer les signaux internes.

Lorsque nous avons abordé pour la première fois le FPGA GameMate A1, nous avons remarqué que Cologne s’appuie sur le framework open source Yosys associé à un outil de placement et de routage propriétaire, mais gratuit, contrairement à la plupart des autres fournisseurs de FPGA qui n’offrent que des outils de développement propriétaires à source fermée. . La société allemande a maintenant publié le projet d’analyseur logique intégré GateMate pour aider les clients à déboguer leurs conceptions FPGA.

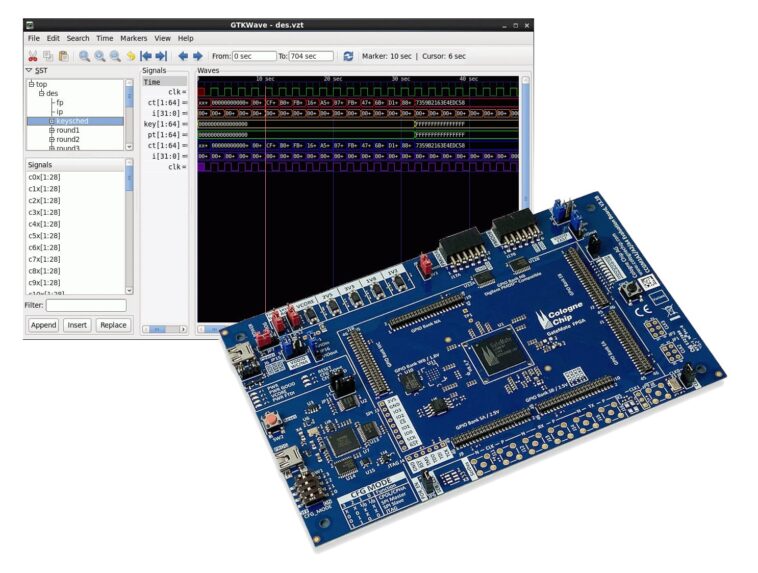

Le projet comprend le circuit numérique de l’ILA conçu dans le langage de description matérielle Verilog et un programme Python (ILA Control Program) utilisé pour configurer la configuration de l’ILA à partir de la conception sous test (DUT) et fournir une interface avec l’utilisateur pendant le processus de débogage. L’utilisateur aura également besoin d’une chaîne d’outils GateMate FPGA et d’un programme open source GTKWave pour visualiser les formes d’onde capturées, ainsi que de sa propre conception FPGA pour le FPGA GameMate ou l’un des exemples de projets (« Blink » ou matrice LED 8×8 ) peut être utilisé à la place.

L’échantillon « Blink » mentionné ici fait référence à une PLL dont le signal d’horloge de sortie incrémente de manière synchrone un registre de 25 bits et ledit registre a son bit de poids fort connecté à une LED. La ligne rouge dans la capture d’écran ci-dessus montre lorsque le bit passe de 0 à 1 et que la LED est allumée.

Le projet a été testé sur la carte d’évaluation FPGA GateMate A1, mais il devrait fonctionner avec des cartes FPGA GateMate conçues sur mesure tant qu’elles répondent à certaines exigences :

si du matériel client est utilisé, veuillez noter que l’ILA nécessite une interface USB entre l’ordinateur et le GateMate FPGA. Le FPGA utilise finalement une interface SPI pour communiquer avec les circuits PCB. L’adaptateur USB vers SPI peut être construit sur le PCB client ou le programmeur GateMate FPGA peut être utilisé et connecté au FPGA.

Vous trouverez l’implémentation de Verilog, des exemples de projets, le programme Python et une documentation détaillée sur la page du projet sur GitHub.

Merci à Dave pour le conseil

Retrouvez l’histoire de Raspberry Pi dans cette vidéo :

-

Qomcsrl Analyseur Logique NanoDLA TYPE-C SCM ARM FPGA 24MHz Taux D'Échantillonnage 8CH Open Source

-

Qomcsrl Kit D'Analyse Logique NanoDLA TYPE-C SCM ARM FPGA, Analyseur de Protocole de Débogage, Fréquence D'Échantillonnage 24 MHz, 8 Canaux, Open Source