ARM Cortex-A320 est un noyau de processeur ARMV9 à faible puissance optimisé pour les applications AI et IoT Edge, avec jusqu’à 50% d’améliorations d’efficacité par rapport au noyau du processeur Cortex-A520. Il s’agit du plus petit noyau Armv9 dévoilé jusqu’à présent.

L’architecture ARMV9 a été introduite pour la première fois en 2021 avec un accent sur l’IA et les noyaux spécialisés, suivis des premiers noyaux ARMV9 – Cortex-A510, Cortex-A710, Cortex-X2 – dévoilés plus tard cette année-là et ciblant les appareils mobiles phares. Depuis lors, nous avons vu des noyaux ARMV9 sur une gamme plus large de smartphones, de cartes mères ARMV9 haut de gamme et de boîtes à télévision, le prochain RockChip RK3688 AIOT SOC comprend également ARMV9 mais cible des applications haut de gamme. Le nouveau ARM Cortex-A320 élargira l’utilisation ARMV9 à une gamme beaucoup plus large de dispositifs IoT, y compris les dispositifs AI Edge limités de puissance.

ARM Cortex-A320 Faits saillants:

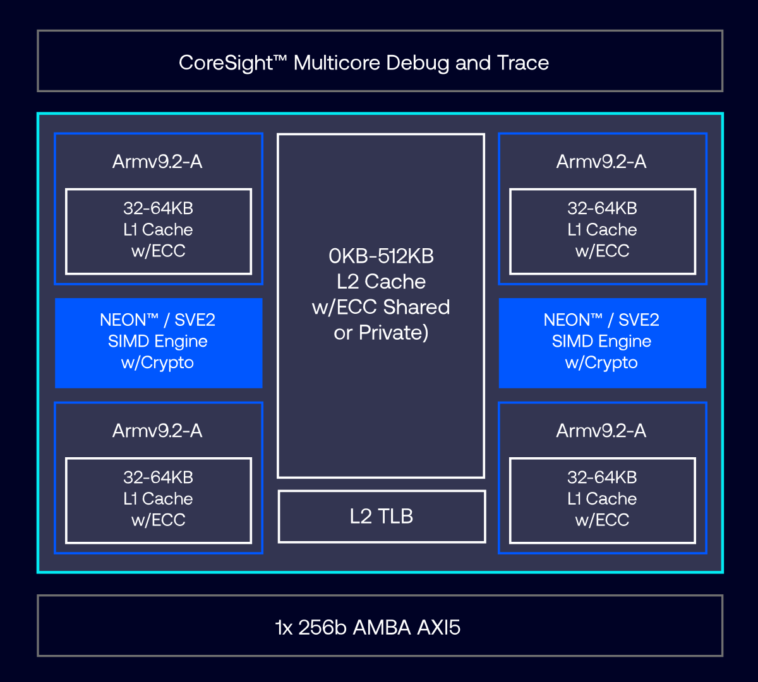

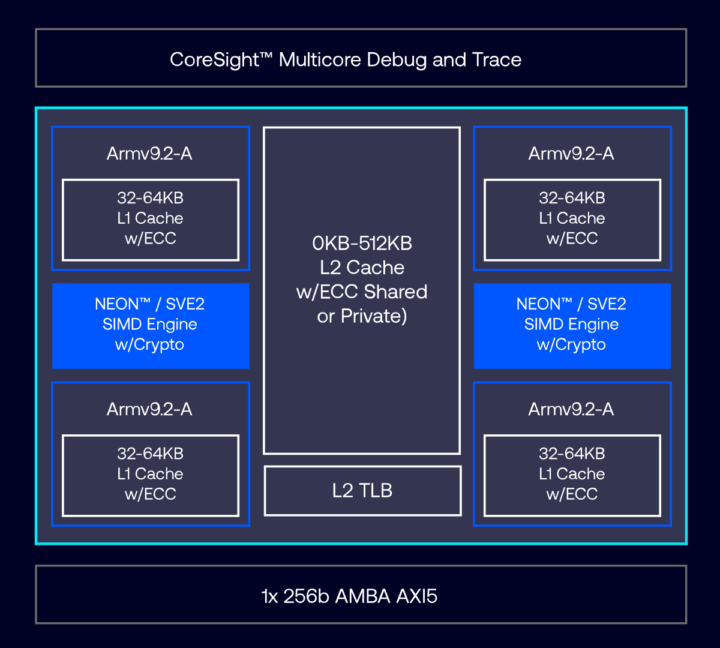

- Architecture – ARMV9.2-A (Harvard)

- Extensions

- Jusqu’à ARMV8.7 Extensions

- Extensions Qarma3

- Extensions SVE2

- Extensions de marquage de mémoire (MTE) (y compris MTE asymétrique)

- Extensions de cryptographie

- Extensions Ras

- Microarchitecture

- Pipeline d’ordre

- Support de superscalar partiel

- Unité de point de point néon / flottant

- Unité de cryptographie facultative

- Jusqu’à 4x CPU en cluster

- Adresse physique 40 bits (PA)

- Système de mémoire et interfaces externes

- 32KB ou 64KB L1 I-cache / d-cache

- Cache L2 en option – 128KB, 192KB, 256KB, 384KB ou 512KB

- Pas de cache L3

- Assistance ECC

- Interfaces de bus – Amba Axi5

- Pas de ACP, pas de port périphérique

- Sécurité – TrustZone, Secure EL2, MTE, PAC / BTI

- Débogage

- Débogage – fonctionnalités ARMV9.2-A

- CORESIGHTV3

- Extension de trace intégrée (EVEV1.1)

- Extension de tampon de trace

- Mission

- Interruptions – Interface GIC, GICV4.1

- Minuterie générique – armv9.2-a

- PMUV3.7

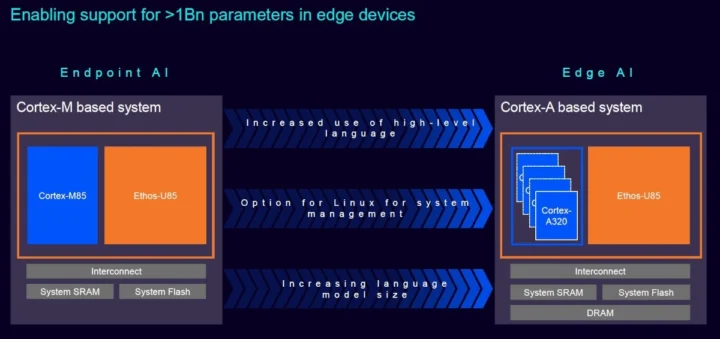

Le Cortex-A320 peut être combiné avec la NPU d’éthos-U85 pour AI Edge, fournissant un chemin de mise à niveau vers les appareils de point de terminaison basés sur l’éthos-U85 Cortex-M85 +, et les systèmes d’exploitation Linux ou Android, en plus de RTOSE comme Freertos ou Zephyr OS. On nous dit également qu’un quad-core Cortex-A320 peut exécuter jusqu’à 256 GOPS, mesurés en Mac / cycle 8 bits lors de l’exécution à 2 GHz.

Outre les améliorations de l’efficacité à 50% par rapport au Cortex-A520, ARM indique que les performances du Cortex-A320 se sont améliorées de plus de 30% dans SCEPINT2K6, par rapport à son prédécesseur ARMV8, le Cortex-A35 grâce à des prédicteurs de branche et des pré-frêtres efficaces et des améliorations du système de mémoire.

Le Cortex-A320 utilise également des améliorations néon et SVE2 dans l’architecture ARMV9 pour offrir jusqu’à 10x meilleures performances d’apprentissage automatique (ML) par rapport au Cortex-A35, ou jusqu’à 6x performances ML plus élevées que le Cortex-A53. Avec ces améliorations de ML et l’efficacité élevée de la surface et de l’énergie, ARM affirme que l’ARM Cortex-A320 est le noyau le plus efficace dans les applications ML dans tous les processeurs ARM Cortex-A.

Renesas peut être l’une des premières sociétés à lancer un SOC ARM Cortex-A320 probablement en 2026, car ils sont l’un des rares partenaires mentionnés dans le communiqué de presse, et ils ont été les premiers à introduire un microcontrôleur ARM Cortex-M85, plus d’un an après le dévoilement. Plus de détails sur le noyau du processeur Cortex-A320 peuvent également être trouvés sur un article de blog et un site Web de développeur d’ARM.

Retrouvez l’histoire de Raspberry Pi dans cette vidéo :

-

BODYA AM4 AMD Kit de support de montage pour Corsair Hydro H55 H75 H80I V2 H100i V2 H115i H90 H105