CNXSoft : Il s’agit d’un article invité de Dave Fohrn, ingénieur logiciel embarqué chez Cologne Chip AG, qui détaille l’analyseur logique intégré (ILA) open source de la société pour les puces FPGA GateMate.

Un réseau de portes programmables sur site (FPGA) est un circuit intégré très flexible dans lequel des circuits logiques complexes peuvent être configurés. Ils sont souvent utilisés comme unités de calcul personnalisées dans les circuits numériques en raison de leur capacité à traiter les données rapidement et en parallèle à l’aide de circuits configurés individuellement.

Les circuits numériques conçus spécifiquement pour les FPGA sont généralement développés dans un langage de description de matériel tel que Verilog ou VHDL et sont appelés gateware. Le terme « porte » fait référence aux unités logiques numériques configurables dans le FPGA sur lesquelles les circuits de porte individuels sont implémentés. Une conception efficace peut accélérer le processus informatique en utilisant stratégiquement les différentes ressources disponibles dans le FPGA, en traitant les données en parallèle et en mettant en œuvre un pipeline intelligent.

Un analyseur logique, un outil courant en technologie numérique, peut être utilisé pour enregistrer et analyser des signaux numériques dans des circuits électroniques. Généralement, un analyseur logique est connecté aux broches externes de composants tels que des FPGA ou des microcontrôleurs pour enregistrer les niveaux de signaux électroniques à une fréquence d’échantillonnage réglable. Les déclencheurs sont définis pour capturer une période de temps spécifique autour d’un événement défini, en réponse à des événements tels qu’un changement de niveau de signal ou l’apparition d’un modèle de signal spécifique. Après avoir enregistré toutes les valeurs échantillonnées autour d’un événement déclencheur, l’utilisateur peut analyser les niveaux de signal sous forme d’onde.

Un analyseur logique intégré (ILA) est implémenté directement en tant que gateware dans un FPGA et permet d’évaluer les formes d’onde de signal internes du gateware à tester (Design Under Test, DUT en abrégé) directement dans le FPGA. Le gateware ILA est connecté aux signaux DUT à analyser et à configurer avec le DUT sur un FPGA. Cela permet aux développeurs de surveiller le comportement des signaux internes de leur gateware dans des conditions réelles, sans affecter le fonctionnement normal du DUT. La durée d’acquisition du signal DUT autour d’un événement déclencheur donné est limitée par les ressources matérielles disponibles dans le FPGA. Cependant, avec un ILA, un événement déclencheur peut être capturé pendant n’importe quelle durée et répété aussi souvent que nécessaire. Cela fournit des informations approfondies pour mieux comprendre et optimiser la fonctionnalité des systèmes complexes.

Dans les environnements réels, des pannes complexes surviennent souvent et ne peuvent pas être détectées par des simulations. Les simulations temporelles post-implémentation, qui tentent de simuler le portail de la manière la plus réaliste possible, nécessitent des calculs extrêmement gourmands et peuvent s’écarter de la réalité. En particulier lorsque le gateware est exploité aux limites de ses spécifications, les problèmes de synchronisation et la dégradation de l’intégrité du signal ne sont pas rares. De plus, des facteurs externes tels que le bruit et les variations de température peuvent modifier le comportement du système. Il est également possible que des événements inattendus surviennent en périphérie du FPGA et n’aient pas été pris en compte dans la simulation. Un ILA peut être utilisé spécifiquement pour identifier de telles erreurs, difficiles à simuler.

Cologne Chip propose désormais un ILA spécialement conçu pour le FPGA GateMate. L’ILA offre un ensemble complet de fonctionnalités pour prendre en charge à la fois le développement de Gateware et la mise en œuvre du GateMate FPGA dans des systèmes complexes.

Portail

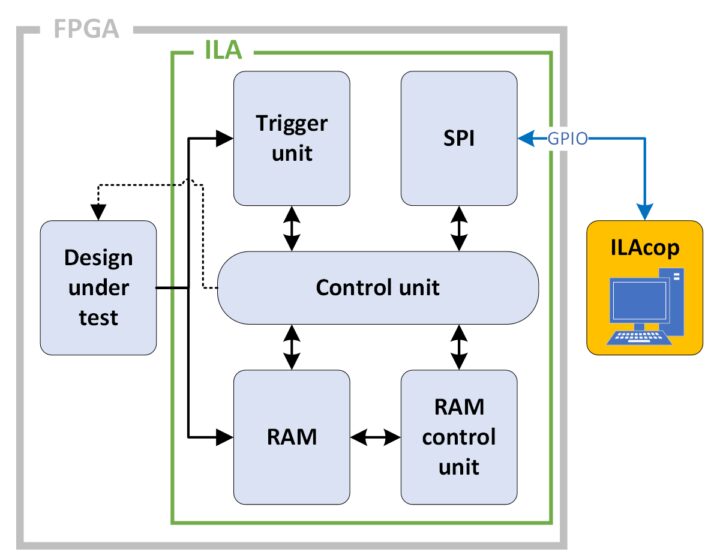

Avec les composants illustrés à la figure 1, le gateware de l’ILA utilise efficacement une partie minimale des ressources matérielles disponibles dans le FPGA. Cela permet à l’ILA d’être configuré en parallèle avec un DUT gourmand en ressources sur le FPGA sans affecter son fonctionnement normal.

Les signaux de test sélectionnés par l’utilisateur sont combinés dans un vecteur de test et connectés à la fois à la RAM et à l’unité de déclenchement. Une fois que le vecteur de test a été synchronisé par un nombre de niveaux de registre sélectionnable par l’utilisateur, il est envoyé directement à l’entrée de données de la RAM. La RAM de l’ILA est flexible en termes de largeur et de profondeur des données et est intégrée au FPGA à partir de cellules Block RAM. Dans l’unité de déclenchement, le vecteur de test est vérifié pour la condition de déclenchement définie.

Le logiciel d’application appelé ILAcop (ILA control program) est installé sur le système d’exploitation du PC de l’utilisateur et permet à la fois la configuration du gateware ILA avant la mise en œuvre et le contrôle du gateware ILA au moment de l’exécution via l’interface périphérique série (SPI en abrégé ). Par défaut, l’ILA utilise une interface USB pour la connexion au PC de l’utilisateur et une puce FTDI pour la traduction USB vers SPI, qui est utilisée à la fois sur la carte d’évaluation de puce de Cologne et dans l’adaptateur de programmation GateMate pour télécharger le flux de données de configuration. Cela présente l’avantage que la configuration matérielle peut être utilisée pour l’analyse une fois le FPGA configuré sans aucune modification.

L’unité de contrôle coordonne la communication avec ILAcop. Il configure le déclencheur à définir dans l’unité de déclenchement, maintient le DUT dans l’état de réinitialisation si nécessaire et démarre le processus d’acquisition de données.

L’unité de contrôle RAM est chargée de garantir que les valeurs échantillonnées du vecteur de test sont disponibles pendant la période de temps définie autour de l’événement déclencheur défini après l’acquisition des données. À cette fin, le nombre d’échantillons avant et après l’événement déclencheur est calculé et défini lors de la configuration du portail ILA en fonction du taux d’échantillonnage défini et de la durée d’enregistrement définie par l’utilisateur. Pendant l’échantillonnage, l’enregistreur de données est en mode tampon circulaire. Une fois la dernière cellule écrite, la première cellule est écrasée. Lorsque le déclencheur est activé, un compteur est démarré qui compte les échantillons jusqu’au nombre requis en parallèle avec le stockage, puis termine le processus d’acquisition des données.

Après le processus d’acquisition des données, les échantillons stockés sont lus depuis la RAM et transférés en série vers ILAcop via SPI. ILAcop reconstruit la forme d’onde du signal à partir des données reçues et la visualise pour l’utilisateur.

Flux de travail

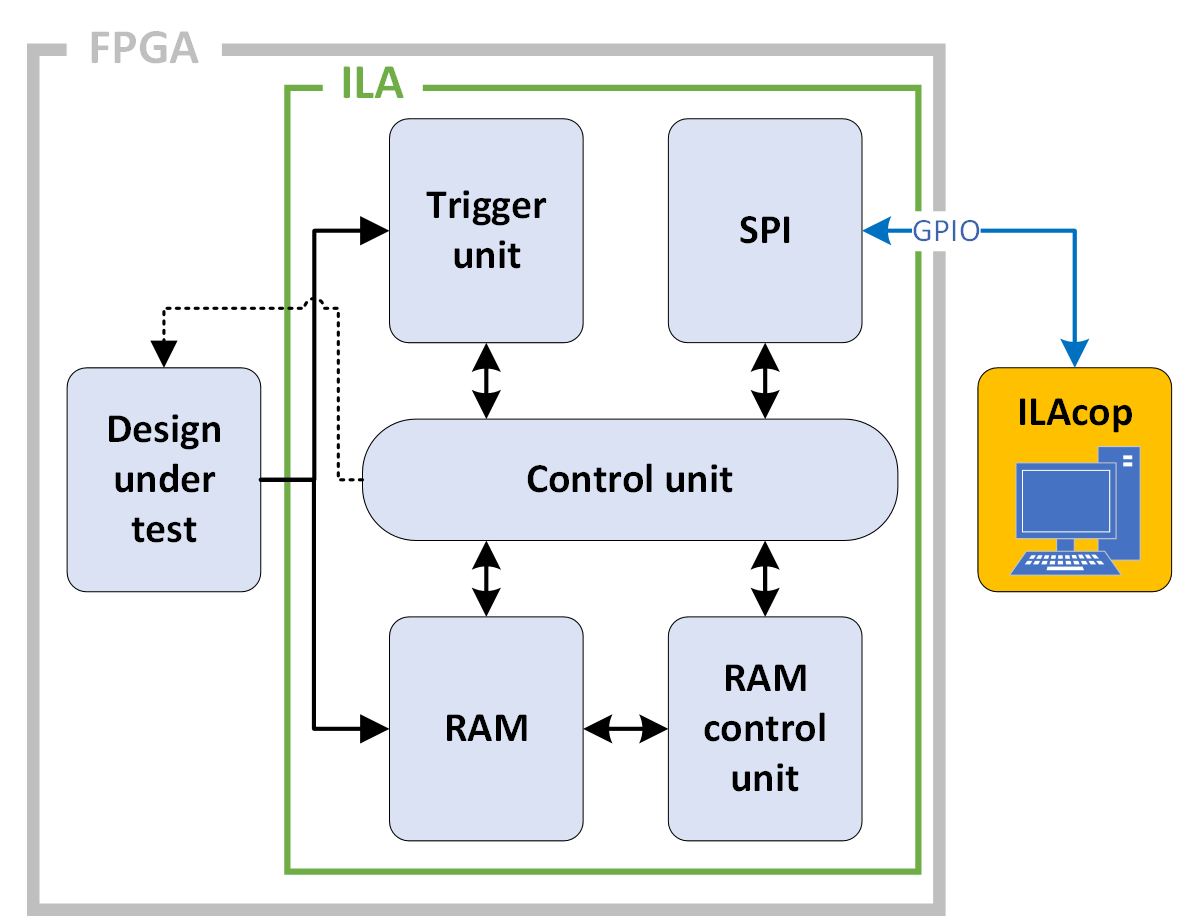

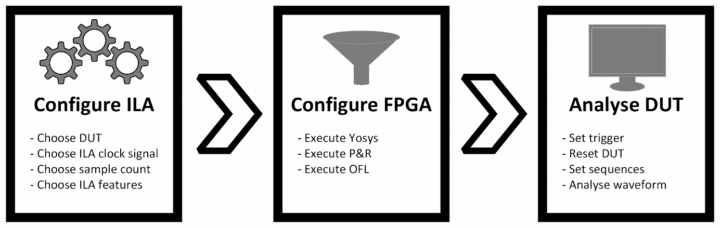

L’ensemble du flux de travail est contrôlé par le programme Python ILAcop. La première étape consiste à configurer le gateware ILA pour chaque DUT. Les configurations telles que la source d’horloge de l’ILA, la durée d’acquisition des données, l’activation des fonctions supplémentaires souhaitées et la sélection des signaux DUT à tester peuvent être effectuées à l’aide de l’assistant de configuration ou lues à partir d’un fichier JSON.

Dans l’étape suivante, les gateware décrits de manière abstraite d’ILA et de DUT, qui sont déjà interconnectés via divers signaux à ce stade, seront configurés sur le FPGA. Tout d’abord, l’ensemble du gateware doit être synthétisé à l’aide de Yosys, un puissant outil de synthèse open source. Au cours du processus de synthèse, le circuit est optimisé et mappé sur les composants matériels spécifiques du GateMate FPGA.

Le placement et l’interconnexion des éléments de circuit sur le FPGA sont ensuite effectués par le logiciel P&R propriétaire de Cologne Chip. Ce logiciel est spécialement conçu pour une gestion efficace de la configuration FPGA et génère un fichier de configuration qui adresse et configure tous les éléments matériels requis pour le gateware dans les FPGA.

Le transfert final des données de configuration vers le FPGA est effectué à l’aide d’OpenFPGAloader, un autre outil open source qui prend spécifiquement en charge le chargement de fichiers de configuration sur un grand nombre de périphériques FPGA.

Une fois le FPGA configuré avec succès, la communication entre ILAcop et le gateware ILA commence. Au moment de l’exécution, l’utilisateur peut utiliser un terminal pour définir les conditions de déclenchement, activer et désactiver la réinitialisation du DUT et démarrer le processus d’acquisition de données.

Après l’acquisition des données, les échantillons stockés sont lus depuis la RAM et transférés en série vers ILAcop via le SPI. ILAcop reconstruit la forme d’onde du signal à partir des données reçues et la visualise pour l’utilisateur.

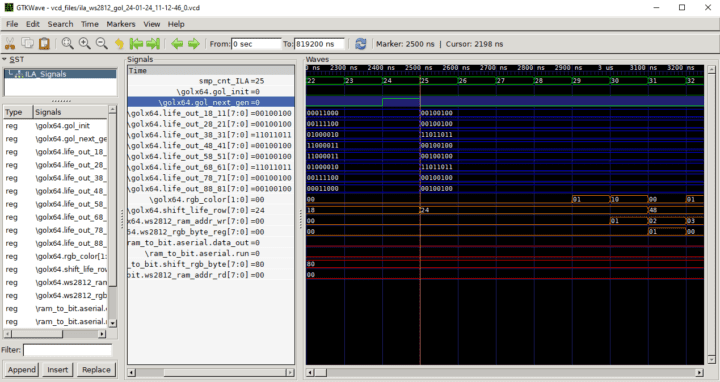

La figure 3 montre une forme d’onde visualisée par GTKWave montrant les signaux d’un DUT du FPGA enregistrés par l’ILA. Alternativement, tout autre visualiseur de formes d’onde avec importation VCD (Value Change Dump) peut être utilisé. La forme d’onde affichée est tirée de l’exemple DUT dans le référentiel Cologne Chip GateMate ILA sur GitHub. L’exemple complet, y compris les explications, peut être trouvé dans le référentiel sous « gatemate_ila/example_dut/ws2812_gol/ ». Les noms de signaux dans le chronogramme sont constitués des modules dans lesquels ils sont définis, organisés hiérarchiquement et séparés par un point et le nom d’origine du DUT.

Caractéristiques du GateMate ILA

- Assistant de configuration : l’utilisateur est guidé tout au long de la configuration de l’ILA pour analyser un DUT par une procédure shell intuitive et facile à utiliser qui fournit des explications pour toutes les configurations.

- Analyse complète du code source du DUT : le système identifie automatiquement la hiérarchie du DUT et recherche dans ses modules, en enregistrant les noms de tous les signaux définis dans la conception. Il recherche également tous les éléments matériels GateMate spéciaux utilisés par le DUT, tels que les PLL ou les Block RAM, et les enregistre pour un traitement ultérieur.

- Sélection flexible et simple d’une fréquence d’échantillonnage : la fréquence d’échantillonnage peut être définie en sélectionnant la sortie d’une PLL supplémentaire avec une fréquence sélectionnable par l’utilisateur, une horloge externe ou une horloge définie dans le DUT, comme la sortie d’une PLL instanciée. .

- Échantillonnage parallèle de plus de 1 000 signaux : les signaux DUT sont sélectionnés par l’utilisateur dans une liste hiérarchique et combinés dans un vecteur de test. Le nombre maximum de bits dans un vecteur de test et le nombre total d’échantillons pouvant être stockés dépendent des cellules Block RAM disponibles dans le FPGA, c’est-à-dire celles non utilisées par le DUT. Le FPGA CCGM1A1 dispose de 32 cellules Block RAM, qui fonctionnent avec le gateware ILA en véritable mode double port. Le nombre d’adresses disponibles et la largeur du bus de données sont configurables de manière variable. Avec une largeur de vecteur de test de 5 bits, jusqu’à 8 192 valeurs échantillonnées peuvent être stockées par cellule de bloc RAM. Si, par exemple, 30 cellules Block RAM sont disponibles pour l’ILA, un total de 245 760 valeurs échantillonnées peuvent être stockées avec une largeur de données de 5 bits. La largeur de données maximale possible d’une cellule Block RAM est de 40 bits, avec 1 024 adresses mémoire disponibles. Avec 30 cellules Block RAM, un vecteur de test peut avoir une largeur maximale de 1 200 bits et un total de 1 024 valeurs échantillonnées peuvent être stockées.

- Configuration de l’ILA à partir d’un fichier JSON : Toutes les configurations créées par l’assistant sont stockées dans un fichier JSON au format texte brut. Cela permet à l’utilisateur d’effectuer facilement des modifications ultérieures, telles que la sélection de différents signaux à analyser. L’utilisation du fichier JSON permet une configuration rapide et facile de l’ILA.

- Déclencheur reconfigurable au moment de l’exécution : grâce à l’interface de communication intégrée de l’ILA, la condition de déclenchement peut être modifiée à tout moment via un programme shell interactif depuis l’ordinateur de l’utilisateur, et le processus d’acquisition de données sur le FPGA peut être démarré ou arrêté sans affecter le fonctionnement. du DUT.

- Fonction de maintien de réinitialisation : Cette fonction permet d’acquérir des signaux immédiatement après que le DUT a quitté l’état de réinitialisation. La réinitialisation du DUT peut être activée ou désactivée selon les besoins avant l’acquisition des données, tandis que la réinitialisation est désactivée dès le démarrage de l’acquisition des données.

- Modèles de bits définis par l’utilisateur comme déclencheurs : L’ILA permet de définir des événements de déclenchement individuels. Une configuration binaire spécifique peut être définie sous forme hexadécimale ou binaire pour être définie comme événement déclencheur attendu sur l’ensemble du vecteur de test. Chaque bit du modèle peut être configuré comme « 1 », « 0 » ou « X » (pour « s’en fiche »). De plus, un déclencheur peut être défini sur n’importe quel signal, déclenché par des événements tels qu’un front montant ou descendant du signal.

- Analyse du signal via la forme d’onde : Une fois que l’événement déclencheur défini s’est produit, la forme d’onde des signaux peut être analysée dans un visualiseur de forme d’onde en utilisant les noms d’origine et les tailles de vecteurs du DUT dans un chronogramme.

- Configuration des séquences d’acquisition de données : Des séquences peuvent être créées avec différentes conditions de déclenchement qui sont exécutées immédiatement les unes après les autres. Cela permet d’enregistrer des valeurs échantillons pour des événements qui se succèdent à de courts intervalles. Dès que les échantillons requis ont été reçus, la condition de déclenchement suivante démarre l’enregistrement. Chaque enregistrement de ces séquences est affiché dans un diagramme temporel distinct.

- Open Source : en tant qu’outil open source, l’ILA offre un haut degré de flexibilité et de personnalisation, ainsi que la possibilité de développement ultérieur par la communauté.

Exemple de configuration ILA avec aperçu de l’utilisation des ressources

La consommation de ressources de l’ILA est variable en raison de sa conception générique et dépend de la configuration. Cela inclut les fonctions définies par l’utilisateur, la largeur de bits du vecteur de test et le nombre d’échantillons requis.

Le DUT possède un seul domaine d’horloge généré par une PLL. Ce domaine d’horloge est défini dans la configuration du gateware ILA pour stocker les échantillons afin de synchroniser le processus d’enregistrement avec le DUT. Cela offre l’avantage que le vecteur de test n’a pas besoin d’être synchronisé avec le domaine d’horloge d’enregistrement ILA avant d’être stocké, et qu’aucune ligne de signal supplémentaire du réseau d’horloge global n’est requise. Dans certains cas, il peut être avantageux de sélectionner une PLL supplémentaire avec une fréquence nettement plus élevée, par exemple pour optimiser les performances ou pour analyser différents réseaux d’horloge et processus asynchrones. Cependant, cela réduira également la durée d’enregistrement maximale possible, car la RAM sera remplie plus rapidement.

Le DUT est réinitialisé à l’aide de la primitive CC_USR_RSTN. La primitive CC_USR_RSTN permet au gateware d’être temporairement réinitialisé immédiatement après la configuration du FPGA. L’ILA a été configuré de telle sorte que le signal de réinitialisation de CC_USR_RSTN puisse également être contrôlé via l’interface SPI, c’est-à-dire que ce signal peut être contrôlé via ILAcop. La fonction de la primitive CC_USR_RSTN est conservée.

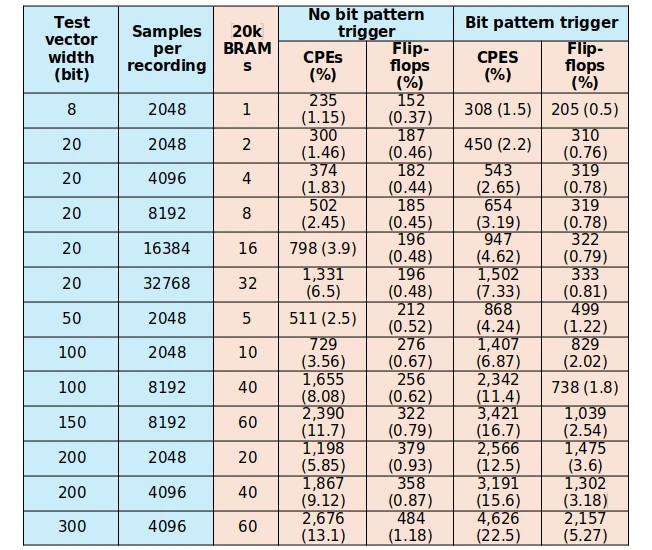

Le test a été réalisé sur la carte d’évaluation V3.1B avec un FPGA CCGM1A1. Le FPGA CCGM1A1 dispose de 64 blocs RAM de 20 000 bits et de 20 480 CPE (éléments programmables de Cologne), chacun avec une arborescence LUT de 8 bits pour les fonctions logiques et deux éléments de mémoire pouvant être utilisés comme bascule ou verrou.

La consommation de ressources de l’ILA sur le FPGA CCGM1A1 est affichée. En fonction de la largeur de bits du vecteur de test et du nombre d’échantillons par enregistrement, la consommation des cellules RAM en bloc (20 000 BRAM), des CPE et des bascules est affichée. Pour chaque configuration, des tests ont été effectués avec et sans modèles de bits définis par l’utilisateur comme déclencheurs.

L’analyse montre une consommation de ressources remarquablement faible. Pour une configuration avec un vecteur de test de 8 bits et un total de 2 048 échantillons par acquisition, seuls 235 CPE sont requis, soit 1,15 % des CPE du plus petit FPGA de la série GateMate. De plus, 152 bascules sont utilisées, ce qui ne représente que 0,37 % du total des bascules disponibles.

Avec la consommation de 60 blocs RAM de 20k, l’ILA a atteint la limite de capacité du total des blocs RAM disponibles sur le FPGA. Sans déclencheurs de configuration binaire, 11,7 % du total des CPE sont utilisés avec une largeur de vecteur de test de 150 bits et 8 192 échantillons, et 13,1 % avec une largeur de vecteur de test de 300 bits et 4 096 échantillons. On peut voir que la consommation de ressources est plus élevée lorsque la largeur du vecteur augmente plutôt que le nombre d’échantillons. Cela devient encore plus clair lorsque le déclenchement de modèle binaire est activé : avec une utilisation maximale de la mémoire, 16,7 % des CPE sont utilisés avec une largeur de vecteur de test de 150 bits et 22,5 % avec une largeur de vecteur de test de 300 bits sur le FPGA CCGM1A1.

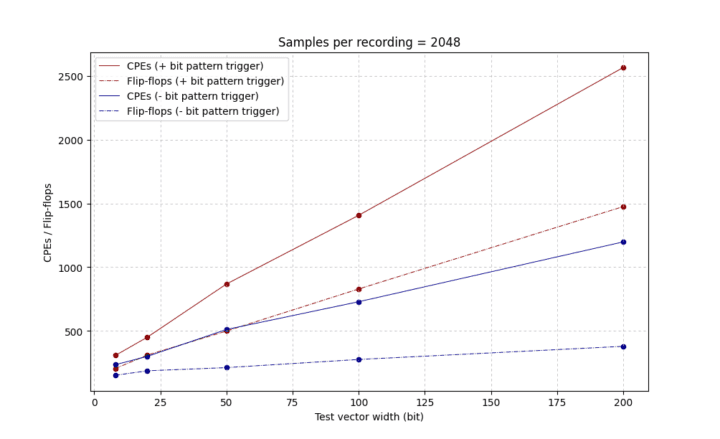

Sur la figure 5, la largeur du vecteur de test est augmentée tandis que le nombre d’échantillons par acquisition reste constant. On voit clairement que la consommation matérielle augmente de manière presque linéaire avec

augmentation de la largeur du vecteur de test. La consommation matérielle augmente beaucoup plus fortement lorsque le déclenchement de modèle binaire est activé.

Conclusion

Le GateMate ILA fournit aux développeurs de gateware pour les FPGA GateMate un outil utile pour analyser en profondeur les signaux de la conception testée dans son environnement de travail réel. Particulièrement

il convient de noter la faible consommation matérielle avec une configuration minimale, permettant à l’ILA d’être implémenté même avec des ressources matérielles très limitées. Une mise en œuvre efficace et l’utilisation de techniques de pipeline minimisent le chemin critique du gateware ILA. Cela permet une analyse même dans les plages de hautes fréquences.

La conception flexible, développée en tant que projet open source, est continuellement améliorée avec des fonctionnalités supplémentaires. Cela rend l’ILA encore plus puissant pour prendre en charge le développement de gateware personnalisés.

Le code source du gateware ILA et d’ILAcop, ainsi que les instructions d’utilisation et d’installation, sont disponibles à l’adresse : https://github.com/colognechip/gatemate_ila.

Retrouvez l’histoire de Raspberry Pi dans cette vidéo :

-

innomaker Analyseur Logique USB LA2016 16 Canaux 200MHz 1G Mémoire avec Logiciel PC en Anglais Portable Haute Vitesse Prise en Charge I2C SPI Can UART pour Windows MacOS Linux

-

Analyseur logique, 16 canaux 400 m de fréquence d'échantillonnage, analyseur de signal numérique avec bande passante de 100 MHz et profondeur de mémoire de 16 G pour analyse de protocole, capture de